# RH850 Debugger and Trace

MANUAL

[TRACE32 Online Help](#)

[TRACE32 Directory](#)

[TRACE32 Index](#)

[TRACE32 Documents](#) .....

[ICD In-Circuit Debugger](#) .....

[Processor Architecture Manuals](#) .....

[RH850](#) .....

[RH850 Debugger and Trace](#) .....

1

[History](#) .....

7

[Introduction](#) .....

8

Available Tools

8

Debugger

8

Software-only Debugger for XCP

8

SFT Trace

9

On-chip Trace

9

High-Speed Serial Off-chip Trace (Aurora NEXUS)

9

Parallel Off-chip Trace (parallel NEXUS)

9

Co-Processor Debugging (GTM)

10

Multicore Debugging

10

Software Installation

10

Related Documents

10

Demo and Start-up Scripts

11

Brief Overview of Documents for New Users

11

[Warning](#) .....

12

[Useful Tips](#) .....

13

Application Starts Running at SYStem.Up

13

Greenhills Compiler

14

Stop Timers and Peripherals during application-break

14

Location of Debug Connector

14

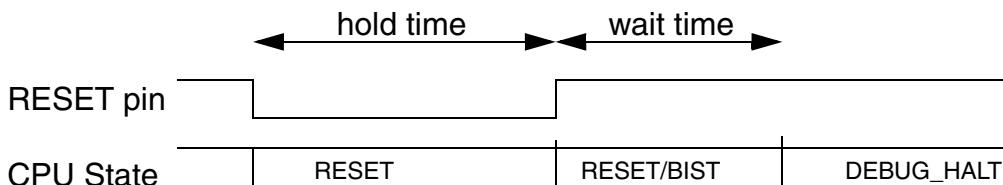

Reset Line

14

Debugging the STOP and DeepSTOP Mode

15

[Configuration](#) .....

16

System Overview

16

[Single Core Debugging - Quick Start](#) .....

17

Debug from Reset

17

|                                                                   |           |

|-------------------------------------------------------------------|-----------|

| Connect to Running Program (Hot Plug-In)                          | 19        |

| <b>Troubleshooting .....</b>                                      | <b>20</b> |

| SYStem.Up Errors                                                  | 20        |

| <b>FAQ .....</b>                                                  | <b>20</b> |

| <b>Debugging .....</b>                                            | <b>21</b> |

| RH850 Debug Interface Modes                                       | 21        |

| JTAG Mode                                                         | 21        |

| LPD4 Mode                                                         | 21        |

| LPD1 Mode                                                         | 22        |

| UART Mode                                                         | 22        |

| Breakpoints                                                       | 24        |

| Software Breakpoints                                              | 24        |

| Onchip Breakpoints                                                | 24        |

| Breakpoint in ROM                                                 | 25        |

| Example for Breakpoints                                           | 25        |

| Access Classes                                                    | 26        |

| Access Classes to Memory and Memory Mapped Resources              | 26        |

| Access Classes to Other Addressable Core and Peripheral Resources | 27        |

| Support for Peripheral Modules                                    | 29        |

| Runtime Measurement                                               | 29        |

| Multicore Debugging                                               | 30        |

| SMP Debugging                                                     | 30        |

| AMP Debugging                                                     | 32        |

| <b>FLASH Programming Support .....</b>                            | <b>34</b> |

| <b>Tracing .....</b>                                              | <b>36</b> |

| SFT Trace via LPD4                                                | 36        |

| NEXUS On-chip Trace                                               | 36        |

| External Trace Ports (Parallel NEXUS/Aurora NEXUS)                | 36        |

| Tracing the Program Flow                                          | 37        |

| Tracing of Data (read/write) Transactions                         | 38        |

| Example: Data Trace with Address Range                            | 38        |

| Trace Filtering and Triggering with Debug Events                  | 39        |

| Event Breakpoints                                                 | 39        |

| Overview                                                          | 39        |

| Example: Selective Program Tracing                                | 40        |

| Example: Event Controlled Program/Data Trace Start and End        | 41        |

| Example: Event Controlled Trace Recording                         | 42        |

| Example: Event Controlled Trigger Signals                         | 42        |

| Example: Event Counter                                            | 43        |

| Tracing Peripheral Modules / Bus Masters                          | 43        |

| <b>SFT Software Trace .....</b>                                   | <b>44</b> |

|                                                  |                                                 |

|--------------------------------------------------|-------------------------------------------------|

| SFT Software Trace to On-chip Trace              | 44                                              |

| SFT Software Trace via LPD4 debug port           | 45                                              |

| <b>CPU specific SYStem Commands .....</b>        | <b>46</b>                                       |

| SYStem.BAUDRATE                                  | Baudrate setting                                |

| SYStem.CONFIG.state                              | Display target configuration                    |

| SYStem.CONFIG                                    | Configure debugger according to target topology |

| Daisy-Chain Example                              | 49                                              |

| TapStates                                        | 50                                              |

| SYStem.CONFIG.CORE                               | Assign core to TRACE32 instance                 |

| SYStem.CONFIG.DEBUGPORT                          | Select target interface                         |

| SYStem.CONFIG.DEBUGPORTTYPE                      | Select debug port type                          |

| SYStem.CONFIG.EXTWDTDIS                          | Disable external watchdog                       |

| SYStem.CONFIG.PortSHaRing                        | Control sharing of debug port with other tool   |

| SYStem.CORECLOCK                                 | Core clock frequency                            |

| SYStem.CPU                                       | CPU type selection                              |

| SYStem.JtagClock                                 | JTAG clock selection                            |

| SYStem.LOCK                                      | Lock and tristate the debug port                |

| SYStem.MemAccess                                 | Select run-time memory access method            |

| SYStem.Mode                                      | System mode selection                           |

| SYStem.OSCCLOCK                                  | Oscillator clock frequency                      |

| SYStem.RESetOut                                  | Reset target without reset of debug port        |

| <b>CPU specific SYStem.Option Commands .....</b> | <b>59</b>                                       |

| SYStem.Option.CFU                                | CalibrationFunctionUnit support                 |

| SYStem.Option.DOWNMODE                           | Behavior of SYStem.Mode Down                    |

| SYStem.Option.DUALPORT                           | Implicitly use run-time memory access           |

| SYStem.Option.FLMD0                              | FLMD0 pin default level                         |

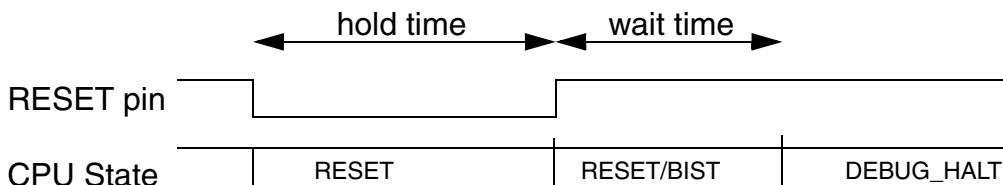

| SYStem.Option.HoldReset                          | Set reset hold time                             |

| SYStem.Option.ICUS                               | ICU-S enable                                    |

| SYStem.Option.IDSET                              | Program KeyCodes to CPU option bytes            |

| SYStem.Option.IMASKASM                           | Interrupt disable                               |

| SYStem.Option.IMASKHLL                           | Interrupt disable                               |

| SYStem.Option.KEYCODE                            | Keycode (G3Kx cores only)                       |

| SYStem.Option.MACHINESPACES                      | Address extension for guest OSes                |

| SYStem.Option.OCDID                              | OnChipDebugID setting                           |

| SYStem.Option.CFID                               | CodeFlashID setting                             |

| SYStem.Option.DFID                               | DataFlashID setting                             |

| SYStem.Option.OPtionByTe                         | Option-byte setting                             |

| SYStem.Option.OPtionByTe8                        | Option-byte setting                             |

| SYStem.Option.CIDA                               | Customer-ID A setting                           |

| SYStem.Option.CIDB                               | Customer-ID B setting                           |

| SYStem.Option.CIDC                               | Customer-ID C setting                           |

| SYStem.Option.PERSTOP                            | Disable CPU peripherals if stopped              |

| SYStem.Option.RESetBehavior                      | Set behavior when target reset detected         |

|                                               |                                                  |           |

|-----------------------------------------------|--------------------------------------------------|-----------|

| SYStem.Option.ResetDetection                  | Configure reset detection method                 | 70        |

| SYStem.Option.RDYLINE                         | RDY pin available                                | 70        |

| SYStem.Option.SLOWRESET                       | Timeout for ResetRiseTime                        | 71        |

| SYStem.Option.WaitReset                       | Set reset wait time                              | 71        |

| <b>SYStem.Option (Exception Lines Enable)</b> |                                                  | <b>72</b> |

| SYStem.Option.CPINT                           | CPINT line enable                                | 72        |

| SYStem.Option.REQest                          | Request line enable                              | 72        |

| SYStem.Option.RESET                           | Reset line enable                                | 72        |

| SYStem.Option.STOP                            | Stop line enable                                 | 73        |

| SYStem.Option.WAIT                            | Wait line enable                                 | 73        |

| <b>CPU specific BenchMarkCounter Commands</b> |                                                  | <b>74</b> |

| BMC.<counter>.ATOB                            | Enable event triggered counter start and stop    | 75        |

| BMC.<counter>.EVENT                           | Configure the performance monitor                | 76        |

| BMC.<counter>.TRIGMODE                        | BMC trigger mode                                 | 77        |

| BMC.<counter>.TRIGVAL                         | BMC trigger value                                | 77        |

| <b>CPU specific TrOnchip Commands</b>         |                                                  | <b>78</b> |

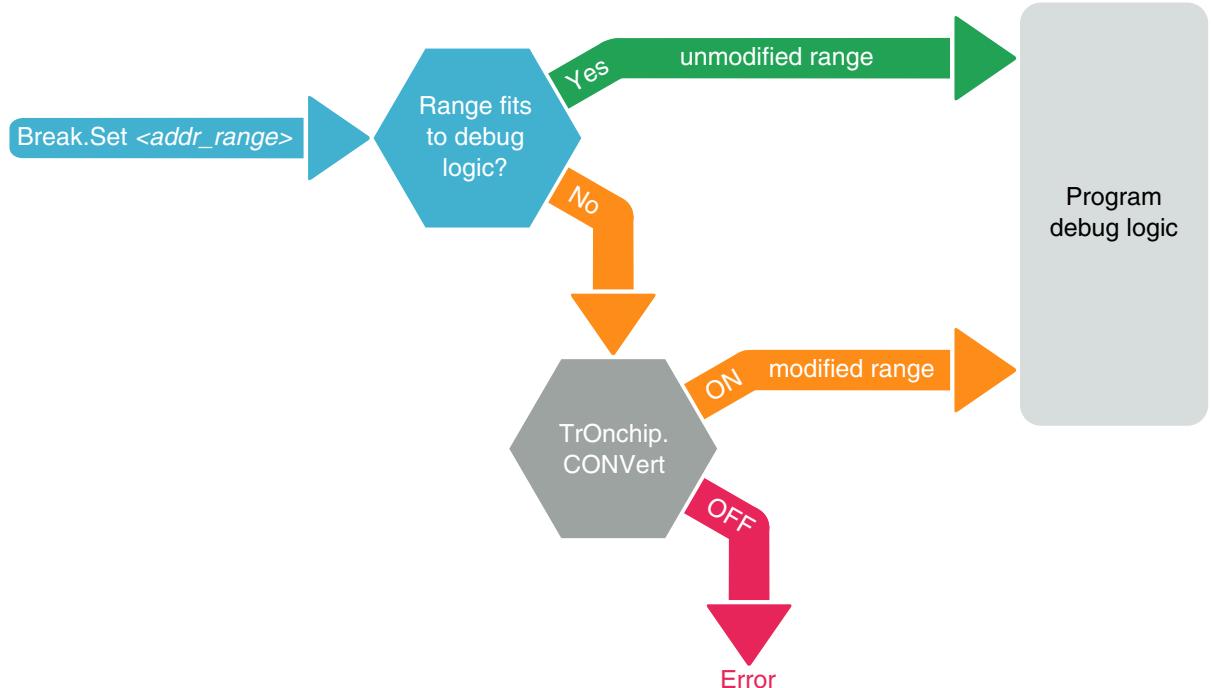

| TrOnchip.CONVert                              | Allow extension of address range of breakpoint   | 78        |

| TrOnchip.EVTEN                                | Enable 'EVTO-' trigger input (Aurora trace only) | 79        |

| TrOnchip.RESet                                | Set on-chip trigger to default state             | 79        |

| TrOnchip.SIZE                                 | Trigger on byte, word, long memory accesses      | 80        |

| TrOnchip.state                                | Display on-chip trigger window                   | 80        |

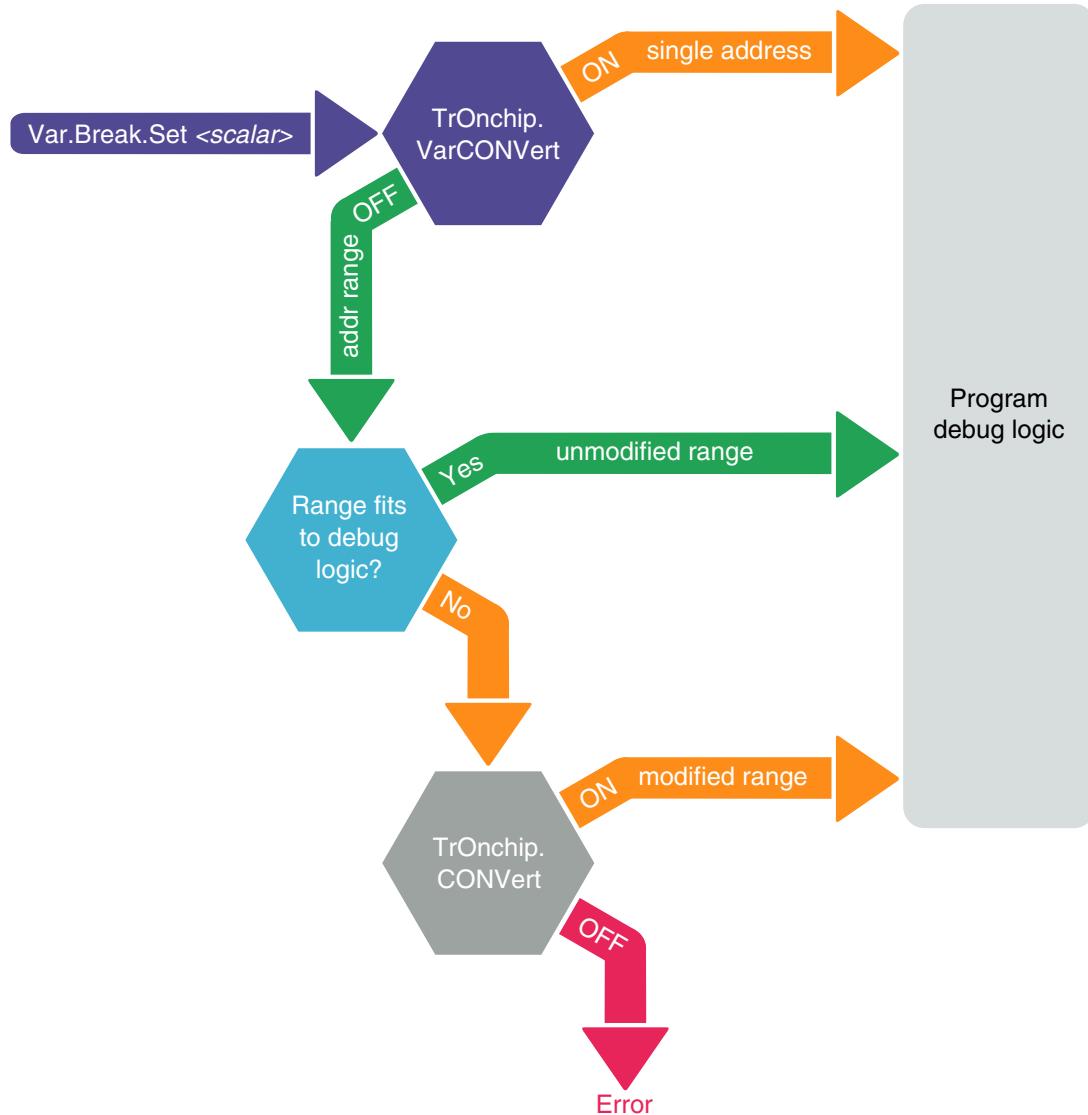

| TrOnchip.VarCONVert                           | Convert breakpoints on scalar variables          | 81        |

| <b>Command Reference: NEXUS</b>               |                                                  | <b>83</b> |

| NEXUS.BTM                                     | Program trace messaging enable                   | 83        |

| NEXUS.CoreENable                              | Core specific trace configuration                | 83        |

| NEXUS.CLIENT<x>.MODE                          | Set data trace mode of nexus client              | 83        |

| NEXUS.CLIENT<x>.SELECT                        | Select a nexus client for data tracing           | 84        |

| NEXUS.DTM                                     | Data trace messaging enable                      | 84        |

| NEXUS.OFF                                     | Disable NEXUS register access                    | 85        |

| NEXUS.ON                                      | Switch the NEXUS trace port on                   | 85        |

| NEXUS.PortMode                                | Set NEXUS trace port frequency                   | 85        |

| NEXUS.PortSize                                | Set trace port width                             | 86        |

| NEXUS.RESET                                   | Reset NEXUS trace port settings                  | 86        |

| NEXUS.SFT                                     | Software trace messaging enable                  | 86        |

| NEXUS.SUSpend                                 | Stall the program execution when FIFO full       | 86        |

| NEXUS.SYNC                                    | Address-sync trace messaging enable              | 87        |

| NEXUS.SyncPeriod                              | Set period of timestamp sync messages            | 87        |

| NEXUS.state                                   | Display NEXUS port configuration window          | 87        |

| NEXUS.TimeStamps                              | On-chip timestamp generation enable              | 88        |

| <b>Nexus specific TrOnchip Commands</b>       |                                                  | <b>89</b> |

| TrOnchip.Alpha                                | Set special breakpoint function                  | 89        |

| TrOnchip.Beta                                 | Set special breakpoint function                  | 90        |

|                                              |                                 |           |

|----------------------------------------------|---------------------------------|-----------|

| TrOnchip.Charly                              | Set special breakpoint function | 90        |

| TrOnchip.Delta                               | Set special breakpoint function | 91        |

| TrOnchip.Echo                                | Set special breakpoint function | 91        |

| <b>CPU specific Functions</b>                |                                 | <b>92</b> |

| CPU.BASEFAMILY()                             | CPU family                      | 92        |

| CPU.DEVICEID()                               | Value of the device-id          | 92        |

| CPU.SUBFAMILY()                              | CPU subfamily                   | 92        |

| SYStem.BAUDRATE()                            | Value of baudrate               | 93        |

| SYStem.CORECLOCK()                           | Core clock frequency            | 93        |

| SYStem.OSCCLOCK()                            | Oscillator clock frequency      | 93        |

| SYStem.CFID()                                | Values of CodeFlashID           | 93        |

| SYStem.DFID()                                | Values of DataFlashID           | 94        |

| SYStem.OCDID()                               | Values of OnChipDebugID         | 94        |

| SYStem.OPBT()                                | Values of Option-bytes          | 94        |

| SYStem.OPBT8()                               | Values of Option-bytes          | 95        |

| SYStem.RESETDETECTION()                      | Reset detection method          | 95        |

| <b>Debug Connector</b>                       |                                 | <b>96</b> |

| Debug Connector 14 pin 100mil                |                                 | 96        |

| Debug Connector 26                           |                                 | 97        |

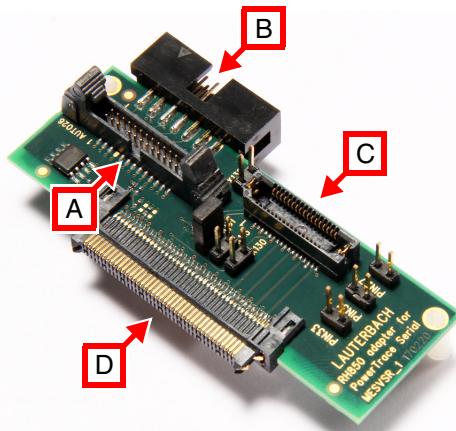

| <b>Trace Connectors and Adapters</b>         |                                 | <b>98</b> |

| Adapter for RH850 (LA-3561)                  |                                 | 98        |

| Parallel NEXUS Connector (Debug and Trace)   |                                 | 100       |

| Aurora NEXUS SAMTEC 34-pin (Debug and Trace) |                                 | 101       |

| Aurora NEXUS SAMTEC 40-pin (Trace only)      |                                 | 102       |

| Aurora NEXUS SAMTEC 46-pin (Debug and Trace) |                                 | 103       |

## History

---

03-Mar-2024 New commands: [SYStem.Option.CIDA](#), [SYStem.Option.CIDB](#), and [SYStem.Option.CIDC](#).

03-May-2023 New command [SYStem.Option.DUALPORT](#).

23-May-2022 New functions: [CPU.BASEFAMILY\(\)](#), and [CPU.SUBFAMILY\(\)](#).

20-May-2022 New functions: [SYStem.BAUDRATE\(\)](#), [SYStem.CORECLOCK\(\)](#), and [SYStem.OSCCLOCK\(\)](#).

20-May-2022 New functions: [SYStem.OPBT\(\)](#), [SYStem.OPBT8\(\)](#), and [SYStem.RESETDETECTION\(\)](#).

19-May-2022 New functions: [CPU.DEVICEID\(\)](#), [SYStem.Option.CFID\(\)](#), [SYStem.Option.DFID\(\)](#), and [SYStem.Option.OCDID\(\)](#).

# Introduction

---

This document describes the processor specific settings and features for RENESAS RH850.

Please keep in mind that only the [Processor Architecture Manual](#) (the document you are reading at the moment) is CPU specific, while all other parts of the online help are generic for all CPUs supported by Lauterbach. So if there are questions related to the CPU, the Processor Architecture Manual should be your first choice.

If some of the described functions, options, signals or connections in this Processor Architecture Manual are only valid for a single CPU or for specific family lines, the name(s) of the family/families is/are added in brackets.

## Available Tools

---

This chapter gives an overview over available Lauterbach tools for the RH850 processors.

### Debugger

---

Debugging RH850 requires a Lauterbach Debug Cable together with a Lauterbach PowerDebug Module.

To connect to the target the following Debug Cable can be used:

- JTAG Debugger for RH850 - LA-3719

The Debug Cable supports all debug interface modes of the RH850 (JTAG, LPD4, LPD1) plus SerialFlashProgramming.

The Debug Cable comes with a license for debugging.

Furthermore it is required to use a Debug Module from the POWER series, e.g.

- POWER DEBUG INTERFACE / USB 3

- POWER DEBUG INTERFACE / USB 2

- POWER DEBUG PRO

The DEBUG INTERFACE (LA-7701) does not support this processor series.

### Software-only Debugger for XCP

---

TRACE32 supports debugging over a 3rd-party tool using the XCP protocol. For details see [“XCP Debug Back-End”](#) (backend\_xcp.pdf).

SFT trace (software trace) requires no extra Lauterbach hardware. Trace data can be saved to the On-chip trace or it can be streamed to the debug box in real time (LPD4 mode only). In streaming mode up to 32MRec of trace data can be recorded.

SFT-trace requires code instrumentation which typically is provided by the compiler tool. TRACE32 reads all SFT-trace symbol information from the loaded ELF file (currently only supported for Greenhills compiler).

Beside the display of SFT string messages, the display of function charts and calculation of runtime-statistics is supported.

## On-chip Trace

---

On-chip tracing requires no extra Lauterbach hardware, it can be configured and read out with the regular debug hardware. On-chip tracing requires a trace license (LA-3734X).

## High-Speed Serial Off-chip Trace (Aurora NEXUS)

---

Lauterbach offers off-chip trace solutions for the Aurora NEXUS trace port. Aurora is a high-speed serial interface defined by Xilinx.

Tracing can either be done with *PowerTrace Serial 4 GigaByte RH850* (LA-3560) which supports up to 8 lanes, each at 12.5Gb/s.

Or with *Preprocessor RH850 HSTP HF-Flex* and a PowerTrace II / PowerTrace III module. This configuration supports up to 4 lanes at a lower speed.

## Parallel Off-chip Trace (parallel NEXUS)

---

Lauterbach offers an off-chip trace solution for processors with parallel NEXUS trace port.

Tracing requires the parallel preprocessor and a POWER TRACE II / POWER TRACE III module.

- Preprocessor Focus II RH850 (LA-3918)

- Preprocessor RH850 (LA-3843)

Debugging the RH850 coprocessors GTM is included free of charge, i.e. there is no additional license required.

For details about coprocessor debugging, see the specific Processor Architecture Manuals:

- [“GTM Debugger and Trace”](#) (debugger\_gtm.pdf)

## Multicore Debugging

---

Lauterbach offers multicore debugging and tracing solutions, which can be done in two different setups: Symmetric Multiprocessing (SMP) and Asymmetric Multiprocessing (AMP). For details see chapter [Multicore Debugging](#).

Multicore debugging of multiple RH850 cores requires the *License for Multicore Debugging (MULTICORE)*.

## Software Installation

---

Please follow chapter [“Software Installation”](#) (icd\_quick\_installation.pdf) on how to install the TRACE32 software:

- An installer is available for a complete TRACE32 installation under Windows. See [“MS Windows”](#) in TRACE32 Installation Guide, page 21 (installation.pdf).

- For a complete installation of TRACE32 under Linux, see [“PC\\_LINUX”](#) in TRACE32 Installation Guide, page 23 (installation.pdf).

## Related Documents

---

- [“GTM Debugger and Trace”](#) (debugger\_gtm.pdf): Debugging and tracing the Generic Timer Module (GTM).

- [“Training Nexus Tracing”](#) (training\_nexus.pdf): Training for the NEXUS trace

- [“Onchip/NOR FLASH Programming User’s Guide”](#) (norflash.pdf): Onchip FLASH and off-chip NOR FLASH programming.

- [“Training Basic SMP Debugging”](#) (training\_debugger\_smp.pdf): SMP debugging.

- [“Application Note Benchmark Counter RH850”](#) (app\_rh850\_bmc.pdf).

- [“XCP Debug Back-End”](#) (backend\_xcp.pdf): Debugging over a 3rd-party tool using the XCP protocol.

# Demo and Start-up Scripts

---

Lauterbach provides ready-to-run start-up scripts for known hardware that is based on RH850.

**To search for PRACTICE scripts, do one of the following in TRACE32 PowerView:**

- Type at the command line: **WELCOME.SCRIPTS**

- or choose **File** menu > **Search for Script**.

You can now search the demo folder and its subdirectories for PRACTICE start-up scripts (\*.cmm) and other demo software.

You can also manually navigate in the `~/demo/rh850/` subfolder of the system directory of TRACE32.

## Brief Overview of Documents for New Users

---

### Architecture-independent information:

- **“Training Basic Debugging”** (training\_debugger.pdf): Get familiar with the basic features of a TRACE32 debugger.

- **“T32Start”** (app\_t32start.pdf): T32Start assists you in starting TRACE32 PowerView instances for different configurations of the debugger. T32Start is only available for Windows.

- **“General Commands”** (general\_ref\_<x>.pdf): Alphabetic list of debug commands.

### Architecture-specific information:

- **“Processor Architecture Manuals”**: These manuals describe commands that are specific for the processor architecture supported by your Debug Cable. To access the manual for your processor architecture, proceed as follows:

- Choose **Help** menu > **Processor Architecture Manual**.

- **“OS Awareness Manuals”** (rtos\_<os>.pdf): TRACE32 PowerView can be extended for operating system-aware debugging. The appropriate OS Awareness manual informs you how to enable the OS-aware debugging.

- **“XCP Debug Back-End”** (backend\_xcp.pdf): This manual describes how to debug a target over a 3rd-party tool using the XCP protocol.

# Warning

---

## Signal Level

---

The debugger output voltage follows the target voltage level. It supports a voltage range of 0.4 ... 5.2 V.

## ESD Protection

---

|                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>WARNING:</b> | <p>To prevent debugger and target from damage it is recommended to connect or disconnect the Debug Cable only while the target power is OFF.</p> <p>Recommendation for the software start:</p> <ol style="list-style-type: none"><li>1. Disconnect the Debug Cable from the target while the target power is off.</li><li>2. Connect the host system, the TRACE32 hardware and the Debug Cable.</li><li>3. Power ON the TRACE32 hardware.</li><li>4. Start the TRACE32 software to load the debugger firmware.</li><li>5. Connect the Debug Cable to the target.</li><li>6. Switch the target power ON.</li><li>7. Configure your debugger e.g. via a start-up script.</li></ol> <p>Power down:</p> <ol style="list-style-type: none"><li>1. Switch off the target power.</li><li>2. Disconnect the Debug Cable from the target.</li><li>3. Close the TRACE32 software.</li><li>4. Power OFF the TRACE32 hardware.</li></ol> |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

## Application Starts Running at SYStem.Up

---

Before TRACE32 can get control of the RH850, the cpu already has started the application startup code.

**This is a restriction of the RH850 core!**

It depends on the executed startup code which peripherals are initialized and if this can cause trouble for the debugging session. E.g.

- enable watchdog

- enter power saving mode

- ECC errors ...

**To prevent unexpected side effects of unwanted code execution at SYStem.Up, an idle-loop should be placed to the reset exception handler.**

What to do:

- Add some “NOP” instructions to the beginning of your “reset exception handler”

- One of the “NOP” instruction addresses should get a label

The “NOP” instructions are just place holders and can stay in your application code.

- For debugging a “jump-to-itself” instruction has to be patched to the “NOP-label” address

**Patching example:**

```

FLASH.ReProgram ALL

Data.LOAD.Elf <file> /<options>           ; load application code

Data.Assemble NOP-label JR $-0                 ; patch jump-to-itself

FLASH.Reprogram OFF

```

- Add the option “**-dual\_debug**” to your compiler/linker settings to generate HLL debug information.

- Add the option “**-No\_Ignore\_Debug\_References**” to your compiler/linker settings in case of missing HLL-Line information in the ELF file.

- Load the code with option **/GHS** example:

```

Data.Load.Elf example.abs /GHS

```

- The compiler can generates HLL line information which points to odd addresses. For TRACE32 the HLL line information and its address has priority, so it can happen the disassembly of certain code lines is terminated. In this case “////////” is displayed. As workaround TRACE32 can ignore such HLL line information. Use command: **sYmbol.CLEANUP.MidInstLines**

- The compiler can generate bitfields in inverted order. Unfortunately the ELF files does not contain any information about the bit order in use. In case of wrong bit-variable display please use the option **/ALTBITLEFIELDS** when loading the code.

```

Data.Load.Elf example.abs /GHS /ALTBITLEFIELDS

```

## Stop Timers and Peripherals during application-break

---

Add following command to your script: **SYStem.Option.PERSTOP ON**

## Location of Debug Connector

---

Locate the debug connector as close as possible to the processor to minimize the capacitive influence of the trace length and cross coupling of noise onto the debug signals.

## Reset Line

---

Ensure that the debugger signal **RESET** is connected directly to the **RESET** of the processor. This will provide the ability for the debugger to drive and sense the status of **RESET**.

# Debugging the STOP and DeepSTOP Mode

---

Ensure the application sets the register WUFMSK0[31] to “0” to enable the TDI debug line as a wake-up factor. This becomes important if the debugger should attach to an already running application which has entered the STOP- or DeepSTOP mode.

TRACE32 displays the message “running (stopmode)” in the state line if the RH850 device enters the STOP- or DeepSTOP-mode. The message will switch to “running (stop occurred)” as soon as there is a wake-up event.

Typically the wake-up is done by the application. Additionally there are several wake-up conditions which are caused by the debugger:

- Break ([Break.direct](#))

- Real-time memory access, e.g.:

- A memory dump in a [Data.dump E:<address>](#) window

- A refresh of a [Var.Watch](#) window

- If breakpoints are changed ([Break.Set](#) or [Break.Delete](#))

- When onchip trace is in ARM mode ([<trace>.Arm](#) or [<trace>.Arm](#))

To prevent unintended wake-ups from the debugger side:

- Set the trace mode to [<trace>.OFF](#) or [<trace>.DISable](#)

- Disable real-time memory access with the command [SYStem.MemAccess Denied](#)

# Configuration

## System Overview

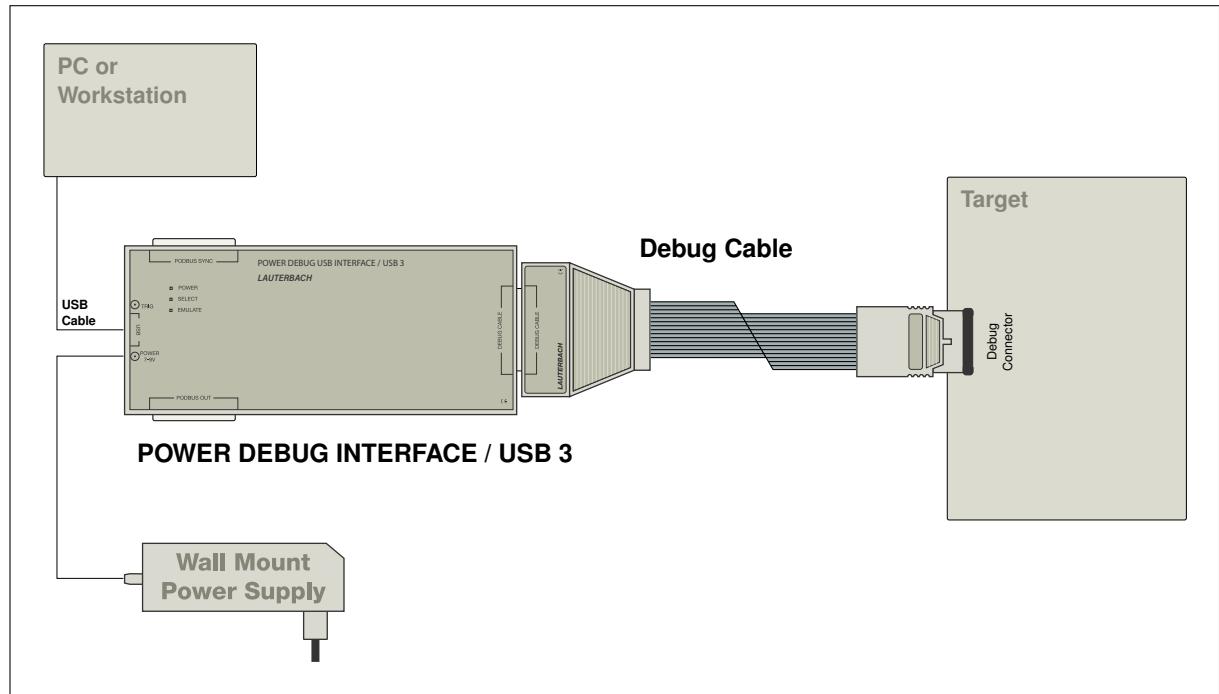

This figure shows an example of how to connect the TRACE32 hardware to your PC and your target board.

# Single Core Debugging - Quick Start

---

## In this section:

- [Debug from Reset](#)

- [Connect to Running Program \(Hot Plug-In\)](#)

## Debug from Reset

---

Starting up the Debugger is done as follows:

1. Select the device prompt B: for the ICD Debugger, if the device prompt is not active after the TRACE32 software was started.

B :

2. Select the CPU type to load the CPU specific settings.

**SYStem.CPU** R7F701035

3. If the TRACE32-ICD hardware is installed properly, the following CPU is the default setting:

JTAG Debugger for RH850

R7F701035

4. Tell the debugger where's FLASH/ROM on the target.

**MAP.BOnchip** 0x00000000++0x7FFF

This command is necessary for the use of on-chip breakpoints.

5. Enter debug mode

**SYStem.Up**

This command resets the CPU and enters debug mode. After this command is executed, it is possible to access the registers. Set the chip selects to get access to the target memory.

**Data.Set...**

6. Load the program.

**Data.LOAD**.ubrof sieve.d85

; (ubrof specifies the format,

; sieve.d85 is the file name)

The option of the **Data.LOAD** command depends on the file format generated by the compiler. A detailed description of the **Data.LOAD** command is given in the “[General Commands Reference](#)”.

The start-up can be automated using the programming language PRACTICE. A typical start sequence is shown below. This sequence can be written to a PRACTICE script file (\*.cmm, ASCII format) and executed with the command **DO <file>**.

```

B::: ; Select the ICD device prompt

WinCLEAR ; Delete all windows

MAP.BOnchip 0x000000++0x07ffff ; Specify where's FLASH/ROM

SYStem.CPU R7F701035 ; Select the processor type

SYStem.Up ; Reset the target and enter debug

; mode

Data.Load.ubrof sieve.d85 ; Load the application

Register.Set PC main ; Set the PC to function main

Data.List ; Open disassembly window      *)

Register.view /SpotLight ; Open register window      *)

Frame.view /Locals /Caller ; Open the stack frame with

; local variables      *)

Var.Watch %Spotlight flags ast ; Open watch window for variables      *)

PER.view ; Open window with peripheral

; register      *)

Break.Set sieve ; Set breakpoint to function sieve

Break.Set 0x1000 /Program ; Set on-chip breakpoint to address

; 1000 (address 1000 is in FLASH)

; (Refer to the restrictions in

; On-chip Breakpoints.)

Break.Set 0xFEDF8000 /Program ; Set software breakpoint to address

; 0xFEDF8000 (address 0xFEDF8000 is in

; RAM)

```

\*) These commands open windows on the screen. The window position can be specified with the [WinPOS](#) command.

# Connect to Running Program (Hot Plug-In)

Hot plug-in is only supported for JTAG and LPD4 debug mode. Follow these steps to attach the debugger to a running system:

1. Select the right debug-interface mode, set the Debug Cable to tri-state mode and connect it to the target.

```

SYStem.CONFIG.DEBUGPORTTYPE LPD4

SYStem.Mode.NoDebug

```

2. Select the target processor.

```

SYStem.CPU R7F701035

```

3. Load debug symbols.

```

Data.LOAD.ELF project.x /NoCODE

```

4. Start debug session without resetting core.

```

SYStem.Mode.Attach

```

5. Observe variables or memory.

```

Var.View %E my_var your_var

Data.Dump E:0x40000100

```

6. Set breakpoints or halt core.

```

Break.Set my_func /Onchip

```

```

Break

```

7. Display ASM/HLL core at current instruction pointer

```

List

```

For information about SMP and AMP debugging, see “[Multicore Debugging](#)”, page 30.

## SYStem.Up Errors

---

The **SYStem.Up** command is the first command of a debug session where communication with the target is required. If you receive error messages while executing this command this may have the following reasons.

|     |                                                                                                                                          |

|-----|------------------------------------------------------------------------------------------------------------------------------------------|

| All | The target has no power.                                                                                                                 |

| All | The target is in reset:<br>The debugger controls the processor reset and use the RESET line to reset the CPU on every <b>SYStem.Up</b> . |

| All | There are additional loads or capacities on the debug lines.                                                                             |

| All | DEBUGPORTTYPE selection does not match the Debug-Interface-Mode setting of the OptionBytes.                                              |

| All | Wrong OSCCLOCK, CORECLOCK or BAUDRATE setting (LPD4, U, CSI mode)                                                                        |

| All | JTAG clock (JTAG mode) too high.                                                                                                         |

## FAQ

---

Please refer to <https://support.lauterbach.com/kb>.

## RH850 Debug Interface Modes

---

The RH850 offers three Debug Interface Modes (JTAG, LPD1, LPD4) plus the SerialFlashProgramming mode by use of the same debug connection.

- The DebugInterface modes are selected by the setting of the CPU OptionBytes.

- The SerialFlashProgramming mode is activated by the voltage level at pin FLMD0.

TRACE32 supports all debug interface modes and SerialFlashProgramming mode.

If TRACE32 can not connect to the CPU it might be necessary to modify the Option-Byte settings or the TRACE32 “DebugPortType” setting. Option Byte programming can be done in SerialFlashProgramming mode only (see below).

**NOTE:**

- Option-Bytes programming is only supported in SerialFlashProgramming mode (UART)!

- UserBootMat FlashProgramming is only supported in SerialFlashProgramming mode (UART)!

### JTAG Mode

---

- Full debug/trace support

- Scripts can be found in the `~/demo/rh850/flash`, `~/demo/rh850/compiler` and `~/demo/rh850/hardware` folders

- CPU-limitation: No flashprogramming of the UserBootMat, no OptionByte programming

- TRACE32 command: **SYStem.CONFIG DEBUGPORTTYPE JTAG** (default)

### LPD4 Mode

---

- Same functions/limitations as in JTAG mode

- TRACE32 command: **SYStem.CONFIG DEBUGPORTTYPE LPD4**

- Interface baud rate has to be defined with command **SYStem.BAUDRATE <value>**

## LPD1 Mode

---

- Same functions/limitations as in JTAG mode

- TRACE32 command: **SYStem.CONFIG DEBUGPORTTYPE LPD1**

- Interface baud rate is detected/configured automatically

- There are RH850 CPU versions which do not support LPD1 mode!

## UART Mode

---

- For serial flash programming and OptionByte programming (**no debugging!**)

- All CPU internal flashes can be programmed

TRACE32 is configured with the commands:

- **SYStem.CONFIG DEBUGPORTTYPE** UART/UART1

- **SYStem.Mode Prepare**

- Special **FLASH.List** table (differs in programming method)

### **Setup script: use pull down RH850->AutoSetup->AutoSetup for SerialFlashProgramming**

The script opens a dialog window which asks for some target-specific parameters

- OSC clock (target-crystal)

- CPU clock (cpu-system-clock)

- UART baud rate

In the scripts you can find some example setting which were working well with the Renesas evaluation boards.

Before flash and/or Option-Byte programming, please verify serial communication works well.

### **Check communication**

After command **SYStem.Mode Prepare**

- Use pull-down-menu “view\message-area”.

- Check the messages of the AREA window.

- The SIGNATURE line shows the detected CPU type (e.g. “R7F701Z00”).

- If the SIGNATURE is wrong --> check clock and baud rate settings and try again.

## OptionByte Programming

The Option-Bytes are described in the CPU User Manual. For programming use command:

**SYStem.Option.OPBT <opbt0>....<opbt7>**

**RH850/F1x --> OPBT0**, bit30 and bit29 (JTAG=y11, LPD1=y10, LPD4=y01)

**RH850/E1x --> OPBT2**, bit30 and bit29 (JTAG=y11, LPD1=y10, LPD4=y01)

The Option-Bytes are programmed immediately, they become effective at the next RESET (**SYStem.Up**).

**NOTE:**

SerialFlash-Programming mode is only needed if the Option-Bytes or UserBootFlash has to be modified. All other debugging stuff and flash programming can be done in JTAG, LPD1 or LPD4 mode.

**RH850/F1x WS1.0 and RH850/E1x FCC (R7F701Z00)** do not support Flash-READ in SerialFlash-Programming mode!

# Breakpoints

---

There are two types of breakpoints available: Software breakpoints (SW-BP) and on-chip breakpoints (HW-BP).

## Software Breakpoints

---

Software breakpoints are the default breakpoints. A special breakcode is patched to memory so it only can be used in RAM or FLASH areas. There is no restriction in the number of software breakpoints.

## Onchip Breakpoints

---

Each core of a RH850 device is equipped with 12 Onchip breakpoints. These breakpoints only can be set if the RH850 has stopped program execution.

The following list gives an overview of the usage of the on-chip breakpoints by TRACE32:

| Number of Onchip-Breaks              | ProgramBreaks                               | Read/Write Breaks                                                                                         | DataValue Breaks                                                                          |

|--------------------------------------|---------------------------------------------|-----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| 12 for each Processor-Element (core) | 12<br>range as bitmask<br>- include/exclude | 4<br>range as bitmask<br>break before make<br><br>- include/exclude<br>- read/write<br>- size ANY/8/16/32 | 4 (G3-cores, break before make)<br>8 (G4-cores, break after make)<br><br>range as bitmask |

With the command **MAP.BOnchip <range>** it is possible to inform the debugger about ROM (FLASH,EPROM) address ranges in target. If a breakpoint is set within the specified address range the debugger automatically uses the available on-chip breakpoints.

## Example for Breakpoints

---

The following breakpoint combinations are possible.

Software breakpoints:

```

Break.Set 0x100000 /Program ; Software breakpoint 1

Break.Set 0x101000 /Program ; Software breakpoint 2

```

On-chip breakpoints:

```

Break.Set 0x100 /Program ; On-chip breakpoint 1

Break.Set 0x0ff00 /Program ; On-chip breakpoint 2

```

# Access Classes

---

Access classes are used to specify how TRACE32 PowerView accesses memory, registers of peripheral modules, addressable core resources, coprocessor registers and the [TRACE32 Virtual Memory](#).

Addresses in TRACE32 PowerView consist of:

- An access class, which consists of one or more letters/numbers followed by a colon (:)

- A number that determines the actual address

Here are some examples:

| Command:                               | Effect:                                               |

|----------------------------------------|-------------------------------------------------------|

| <b>Data.List P:0x1000</b>              | Opens a List window displaying <b>program</b> memory  |

| <b>Data.dump D:0xFEBF8000 /LONG</b>    | Opens a DUMP window at <b>data</b> address 0xFEBF8000 |

| <b>Data.Set SR:0. %Long 0x00003300</b> | Write value 0x00003300 to system register 0           |

| <b>PRINT Data.Long(D:0xFEBF8000)</b>   | Print data value at physical address 0xFEBF8000       |

## Access Classes to Memory and Memory Mapped Resources

---

The following memory access classes are available:

| Access Class | Description                                          |

|--------------|------------------------------------------------------|

| P            | Program (memory as seen by core's instruction fetch) |

| D            | Data (memory as seen by core's data access)          |

In addition to the access classes, there are access class attributes.

The following access class attributes are available:

| Access Class Attributes | Description                                                                                                                 |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| E                       | Use real-time memory access.<br>This attribute has no effect if <a href="#">SYStem.MemAccess</a> is set to <b>Denied</b> ). |

Examples of usage:

| Command:                       | Effect:                                                                      |

|--------------------------------|------------------------------------------------------------------------------|

| <b>Data.dump ED:0xFEEE0000</b> | Opens dump window at address 0xFEEE0000 using <b>real-time memory access</b> |

If an access class attribute is specified without an access class, TRACE32 PowerView will automatically add the default access class of the used command. For example, **Data.List** E:0x100 is complemented to **Data.List** EP:0x100.

## Access Classes to Other Addressable Core and Peripheral Resources

---

The following access class is used to access system registers which are not mapped into the processor's memory address space.

| Access Class | Description                 |

|--------------|-----------------------------|

| SR           | System Register (SR) access |

The RH850 supports 256 System Registers which are divided into 8 groups (selID) with 32 registers (regID) each.

Example: The ISPR register has a regID==10 and selID==2

Using the **SR**: access class the System Register address is defined by:

- Addressbit(4..0) = regID

- Addressbit(7..5) = selID

So the ISPR register can be accessed by commands:

```

Data.dump SR:0x4A++0 /Long ;dump window showing the ISPR

;register value

PRINT Data.Long(SR:0x4A) ;print ISPR register value to

;status line

Data.Set SR:0x4A %Long 0x11223344 ;set ISPR register with value

;0x11223344

```

The following access class is used to access chip internal debug registers. Use this only if requested by Lauterbach! Accessing debug registers (read or write) without the background knowledge of their functionality may have bad influence for debugging up to TRACE32 crash.

| Access Class | Description                         |

|--------------|-------------------------------------|

| DBG:         | Debug-Register access               |

| EDBG:        | use real-time Debug-Register access |

Each RH850 core (also called ProcessorElement PEx) has it's own set of debug registers. Each set can have up to 8 banks with 256 registers each.

- Address bits(7..0) = IR register number

- Address bit(11..8) = Bank number

- Address bit(12) = select JCU register-set

- Address bit(26..13) = select PE(14..1) register-set

- Address bit(27) = select broadcast access to all assigned cores (for write access only)

- Address bit(31..28) = DBG Sub-Access-Class (set to 0x1 always)

```

Data.Set DBG:0x100024AB %Long 0x12      ;write 0x12 to debug-register:

; - ProcessorElement PE1

; - Bank=0x4

; - IR=0xAB

PRINT Data.Long(EDBG:0x100024AB)      ; - print debug-register value to

;   status line

; - uses real-time access to read

;   the value

```

TRACE32 supports access to the memory mapped registers of all peripheral modules. The peripheral register description files (\*.per, so-called PER-files) for the on-chip peripherals are included in TRACE32. PER files for recent processors are usually not included in updates, but are available upon request.

For external peripherals and/or custom peripherals, it is possible to create additional PER files with custom content. See “[Peripheral Files Programming](#)” (per\_prog.pdf) for details.

## Runtime Measurement

---

If the device is equipped with an Onchip- or Offchip-Trace then typically the trace recordings are used for function-run-time and function-nesting analysis.

For devices without any trace, the Onchip [BenchMarkCounters](#) can be used for core-clock accurate measurements of the min-, max- and average- runtimes. It is also possible to stop the program execution if the runtime exceeds a predefined min- or max- value.

Beside that, the debuggers [RunTime.state](#) window gives detailed information about the complete runtime of the application code and the runtime since the last [Go](#), [Step](#), [Step.Over](#) command. Runtime measurement is done with a resolution of about 5  $\mu$ s.

One or more cores (RENESAS terminology: “ProcessorElement” or “PEx”) can be assigned to a TRACE32 PowerView instance. The cores are referred to by its “ProcessorElement” index PE1 to PE6

TRACE32 supports either controlling each core with a separate PowerView instance ([AMP debugging](#)) or controlling multiple cores with a single PowerView instance ([SMP debugging](#)). SMP debugging is only possible for cores of the same architecture.

TRACE32 also supports mixed AMP/SMP operation. E.g. RH850/P1x-C devices can be controlled with two PowerView instances, one for PE5\_core (ICU-M) and one controlling PE1\_core and PE2\_core in SMP mode.

## SMP Debugging

---

In TRACE32 terminology, SMP debugging means to control more than one core in a single PowerView instance. Use this method for cores which run the same kernel / instance of the operating system. Cores controlled in a single PowerView instance share the following resources:

- Debug symbols

- OS Awareness

- Run control ([Go](#), [Step](#), [Break](#)) and breakpoints

- Debug and trace settings

If it is desired to have control over any of the above resources separately for each core, [AMP debugging](#) must be used.

Follow these steps to set up the debugger for SMP debugging:

1. Select the target processor, or use automatic CPU detection.

```

SYStem.DETECT CPU

```

2. Assign cores to this PowerView instance

```

;CORE.ASSIGN <logical_core_0> <logical_core_1> [...]

; assign PE1 to logical_core_0

; assign PE3 to logical_core_1

CORE.ASSIGN 1 3

```

3. Start debug session and continue as usual.

```

SYStem.Up           ; connect to core PE1

SYStem.Mode.Attach ; connect to core PE2

```

All core context dependent windows (Register, List, Dump, etc.) show the data as seen from the currently selected core. Select a core using the command **CORE.select <logical\_core\_index>**.

```

Register

CORE 0      ;Register window shows registers of PE1

CORE 1      ;Register window shows registers of PE3

```

If any of the cores hits a breakpoint, PowerView automatically selects the core that hit the breakpoint. The currently selected core displayed in the status bar and can be changed by right-clicking on the core field.

It is also possible to show more than one core context at the same time, using the option **/Core <logical\_core\_index>**. All windows with core-dependent information support this option.

```

Register /CORE 0

Register /CORE 1

List /CORE 0

List /CORE 1

```

Example scripts for SMP debugging can be found in the demo folder.

- <~/demo/rh850/hardware/>

Further demo scripts available for download and upon request.

In AMP debugging mode, a separate PowerView instance is started for each core. The individual instances are completely independent of each other, but it is possible to synchronize run-control and system mode changes (see **command SYnch**).

An easy way to start multiple PowerView instances is to use **T32Start**. It is also possible to start further instances from a PRACTICE script.

The following steps demonstrate the setup for AMP debugging, assuming that the application is already programmed to FLASH:

1. Select the target processor, or use automatic CPU detection.

|                                    |                                     |

|------------------------------------|-------------------------------------|

| <code>;core_0 (PE1) script:</code> | <code>; core_1 (PE3) script:</code> |

| <code>SYStem.CPU R7F701Z07</code>  | <code>SYStem.CPU R7F701Z07</code>   |

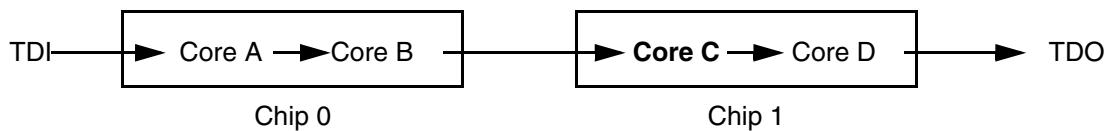

2. Assign target cores to the individual instances. Use either “**SYStem.CONFIG.CORE <core\_index> <chip\_index>**” or “**CORE.ASSIGN <core\_index>**”. The parameter **<chip\_index>** must be the same for all cores on the same chip.

|                                        |                                        |

|----------------------------------------|----------------------------------------|

| <code>; core_0 (PE1) script:</code>    | <code>; core_1 (PE3) script:</code>    |

| <code>SYStem.CONFIG.CORE 1 . 1.</code> | <code>SYStem.CONFIG.CORE 3 . 1.</code> |

3. **SYStem.CONFIG.Slave** must be OFF for the core that starts running right from reset. Set to ON for all other cores (that are released later by the first core).

|                                      |                                     |

|--------------------------------------|-------------------------------------|

| <code>SYStem.CONFIG.Slave OFF</code> | <code>SYStem.CONFIG.SLAVE ON</code> |

|--------------------------------------|-------------------------------------|

4. Load debug symbols on both instances.

|                                       |                                       |

|---------------------------------------|---------------------------------------|

| <code>Data.LOAD appl.x /NoCODE</code> | <code>Data.LOAD appl.x /NoCODE</code> |

|---------------------------------------|---------------------------------------|

5. Start debug session: **SYStem.Up** for the core that runs right from reset. **SYStem.Mode.Attach** for all cores that are started later.

|                        |                                 |

|------------------------|---------------------------------|

| <code>SYStem.Up</code> | <code>SYStem.Mode.Attach</code> |

|------------------------|---------------------------------|

6. Core\_0 is halted at the reset address and core\_1 remains in reset, In order to halt core\_1 as soon as it is released from reset, issue the **Break** command.

|                    |

|--------------------|

| <code>Break</code> |

|--------------------|

7. Start core\_0. Core\_1 will halt at its reset address after being released by core\_0.

Go

WAIT !RUN() ; wait until cpu stops

Example scripts for AMP debugging can be found in the demo folder.

- [~~/demo/rh850/hardware/](#)

Before Flash programming can work TRACE32 has to be informed about the CPU's flash memory mapping. This is done with the demo scripts in the `~/demo/rh850/flash` directory or by use of the TRACE32 AutoSetup.

AutoSetup offers a convenient way to connect to **RH850 single-core devices** and to configure TRACE32 for flash programming.

- Please click the pull-down menu **RH850->AutoSetup**

- Select **AutoSetup for Debugging** or **AutoSetup for SerialFlashProgramming** -> press OK.

- Finally you will be asked if flash-programming should be done

The found configuration can be saved with command: **STOre <file>.cmm SYStem FLASH**

The TRACE32 message area (command **AREA**) presents all information which was read out of the CPU and all executed TRACE32 configuration commands. In case the setup fails, please have a look to the **AREA** window to clarify why it did not work.

**RH850 multi-core devices** often require chip/application specific startup sequences. detection typically fails. Please have a look to the board specific scripts which can be found in the directory `~/demo/rh850/hardware/`

For flash programming use following command sequence:

```

FLASH.ReProgram ALL ; enable flash programming

Data.Load.Elf output/example.abs /GHS ; load application (here

; Greenhills compiler)

Data.Load..... /NoClear ; load more code (optional)

Data.Set... ; patch your code (optional)

FLASH.ReProgram OFF ; start flash-erase/program

; sequence

```

With **FLASH.ReProgram ALL** all code is loaded to a virtual memory first. This means you generate a "flash-image" in virtual memory which can be modified with additional code downloads or code-patches. At the same time the data is compared against the current flash content.

In the **FLASH.List** window all **modified** flash-segments are marked as "pending". Only this flash-segments will be erased/programmed.

If the “flash-image” is complete use command **FLASH.ReProgram OFF**. Then all “pending” segments are erased and reprogrammed. The big advantage of this method is that only modified flash-segments are erased/programmed. Programming is quicker and programming-stress for the FLASH is reduced.

**NOTE:**

**SerialFlashProgramming of “RH850-F1x WS1.0” and “RH850/E1x FCC (R7F701Z00)”**

This devices do not support memory-read in UART mode. As result an UART-Error message is displayed in the **AREA** window. This is just for information and has no effect on flash programming. The **Data.dump** window is grayed out as long as no data is loaded to virtual-memory.

**FlashProgramming and switching of the debug interface mode**

The flash declaration of SerialFlashProgramming mode (UART) is different to the debug modes (JTAG, LPD4, LPD1)! When switching between the modes it is necessary to do a new flash declaration setup (**use RH850->AutoSetup**)!

Processors of RH850 series implement a variety of trace modules. Depending on the module, the trace information is either stored on the processor or sent out through an external trace port. This section lists all available trace modules, their configuration options and examples.

## SFT Trace via LPD4

---

In LPD4 debug interface mode the RH850 can transfer SFT-trace messages (software trace) to the debug box. No extra trace hardware or license is needed.

## NEXUS On-chip Trace

---

Many processors of the RH850 family implement a feature to store the NEXUS messages of cores and peripheral trace clients into an on-chip trace memory.

Using the on-chip trace with just a debug cable (LA-3719) requires the on-chip trace license LA-3734X.

The on-chip trace license is not required if your tool in use contains one of the following parts:

- PowerTrace Serial 4 GigaByte RH850 (LA-3560)

- Serial Preprocessor RH850 (LA-3843)

- Preprocessor Focus II RH850 (LA-3918)

- Preprocessor RH850 (LA-3843)

The configuration of trace methods and clients is done through the **NEXUS** and **TrOnchip** command groups.

## External Trace Ports (Parallel NEXUS/Aurora NEXUS)

---

NEXUS trace messages from cores and peripheral trace clients are conveyed off-chip via an external trace port. External trace ports are only provided by RH850 emulation devices.

Depending on the processor, the messages are sent through a high-speed serial connection (XILINX Aurora protocol) or through the parallel NEXUS AUX interface (MDO, MSEO, MCKO). Lauterbach offers the various trace tools to record and store the trace information

Trace tools for the high-speed serial connection:

- PowerTrace Serial 4 GigaByte RH850 (LA-3560)

- Serial Preprocessor RH850 (LA-3843) in conjunction with PowerTrace II / PowerTrace III

The TRACE32 online help provides a “[PowerTrace Serial User’s Guide](#)” (serialtrace\_user.pdf), please refer to this manual if you are interested in details about PowerTrace Serial.

Trace tools for the parallel NEXUS AUX interface:

- Preprocessor Focus II RH850 (LA-3918) in conjunction with PowerTrace II / PowerTrace III

- Preprocessor RH850 (LA-3843) in conjunction with PowerTrace II / PowerTrace III

The TRACE32 online help provides a “[AutoFocus User’s Guide](#)” (autofocus\_user.pdf), please refer to this manual if you are interested in details about Preprocessor Focus II .

The complete trace port configuration is done by TRACE32 automatically. No special settings are required.

## Tracing the Program Flow

---

Tracing of the program flow is enabled by default.

### Branch Trace Messaging (BTM)

---

This is the default method set in TRACE32. The processor is configured to send a trace message for indirect branches only. Information about direct branches and amount of executed instructions is sent in occasional resource full messages.

Setup of branch trace messaging:

```

NEXUS.BTM ON

NEXUS.SYNC OFF

```

### Synchronization Trace Messaging (SYNC)

---

By default the NEXUS protocol uses an address compression algorithm to reduce the number of bytes per NEXUS message. From time to time a synchronization message is sent which holds the complete (non compressed) address of the program flow. For TRACE32 this message is the start for program flow reconstruction.

All recordings before the synchronization message are ignored because it is not possible to calculate the program flow. There are debug scenarios where you like to get a valid trace listing also for this “ignored” records. In this case the NEXUS.SYNC option can help.

If **ON**, each NEXUS message holds the complete address, the address compression is disabled.

Setup of branch sync tracing:

```

NEXUS.BTM ON

NEXUS.SYNC ON

```

## Note for OnchipTrace (optional bugfix):

There are RH850 devices with a bug in the NEXUS coding for Onchip-Trace. In case of flow-errors in the trace listing please set **NEXUS.SYNC ON** and try again.

## Tracing of Data (read/write) Transactions

---

General data tracing is enabled using the command **NEXUS.DTM**. This command enables the data trace for the full address space. The amount of generated trace messages is usually too high to be sent through the trace port and the on-chip message FIFO will overflow.

The amount of generated trace messages can be reduced by defining address ranges for which data trace is generated. Up to four address ranges are possible.

### Example: Data Trace with Address Range

---

Use **TraceData** to limit the data trace to an address range. Up to 8 address ranges per core are possible. TraceData has no impact on program trace messaging setting.

```

;Enable data trace for read/write accesses to all peripherals

Break.Set 0xC0000000--0xFFFFFFFF /ReadWrite /TraceData

```

```

;In addition to full program trace, enable data trace for read accesses

;to the array flags

NEXUS.BTM ON

Var.Break.Set flags /Read /TraceData

```

Another method of reducing trace data is **event-triggered trace filtering**.

## Event Breakpoints

---

Each core of a RH850 chip is equipped with 16 Event breakpoints. TRACE32 uses them for:

- Trace-recording control: TraceOn, TraceOff, TraceEnable, TraceData, WatchPoints

- Trigger control: TraceTrigger, BusTrigger, BusCount

The following list gives an overview of the usage of the Event breakpoints by TRACE32:

| Number of Event-Breaks               | ProgramBreaks    | Read/Write Breaks | DataValue Breaks      |

|--------------------------------------|------------------|-------------------|-----------------------|

| 16 for each Processor-Element (core) | 8<br>or 4 ranges | 8<br>or 4 ranges  | 8<br>range as bitmask |

Event breakpoints are also supported for other Trace-Clients like GlobalRam, LocalRam, PeripheralBus.

| Number of Event-Breaks | ProgramBreaks | Read/Write Breaks | DataValue Breaks      |

|------------------------|---------------|-------------------|-----------------------|

| 4 for each client      |               | 4<br>or 2 ranges  | 4<br>range as bitmask |

## Overview

---

Any Event Breakpoint can be configured to either trigger a *watchpoint hit message*, or to act as input event for selective tracing. TRACE32 offers a variety of features based on watchpoints.

Event Breakpoints are set using the command **Break.Set**, similar to breakpoints that halt the core, but additionally include an option to define the desired behavior:

**Break.Set <address>|<range> /<action>**

Define trace filter or trigger

The list below shows all available trace filtering and trigger actions:

| <action>                          | Behavior                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>TraceEnable</b>                | Configure the trace source to only generate a trace message if the specified event occurs. Complete program flow or data trace is disabled. If more than one TraceEnable action is set, all TraceEnable actions will generate a trace message.                                                                                                                                                                                                                                                                           |

| <b>TraceON</b><br><b>TraceOFF</b> | If the specified event occurs, program and data trace messaging is started (TraceON) or ends (TraceOFF). In order to perform event based trace start/end to program trace and data trace separately, use Alpha-Echo actions.                                                                                                                                                                                                                                                                                             |

| <b>TraceTrigger</b>               | Stop the sampling to the trace on the specified event. A trigger delay can be configured optionally using <a href="#">Analyzer.TDelay</a> .                                                                                                                                                                                                                                                                                                                                                                              |

| <b>BusTrigger</b>                 | If the specified event occurs, a trigger pulse is generated on the podbus trigger line. This trigger signal can be used to control other podbus devices (e.g. PowerProbe) or to control external devices using the trigger connector of the PowerDebug/PowerTrace module (see <a href="#">TrBus</a> ).                                                                                                                                                                                                                   |

| <b>BusCount</b>                   | The specified event is used as input for the counter of the PowerDebug/PowerTrace module. See <a href="#">Count</a> for more information.                                                                                                                                                                                                                                                                                                                                                                                |

| <b>WATCH</b>                      | Set a watchpoint on the event. The CPU will trigger the EVTO pin if the event occurs and generate a watchpoint hit message if the trace port is enabled.                                                                                                                                                                                                                                                                                                                                                                 |

| <b>Alpha - Echo</b>               | Declares a special trace control / trigger event. The actual event is configured through the <a href="#">TrOnchip</a> window. Two classes of events are supported: <ul data-bbox="360 1030 1271 1106" style="list-style-type: none"><li data-bbox="360 1030 1271 1058">Configure event based trace start/end for program and data separately</li><li data-bbox="360 1068 1271 1096">Configure Trace/Trigger events for additional nexus trace clients</li></ul> See <a href="#">TrOnchip.Alpha</a> for more information. |

## Example: Selective Program Tracing

**TraceEnable** enables tracing exclusively for the selected events. All other program and data trace messaging is disabled.

```

;Only generate a trace message when the instruction

;at address 0x00008230 is executed.

Break.Set 0x00008230 /Program /TraceEnable

```

**TraceEnable** can also be applied on data trace:

```

;Only generate a trace message when the core writes to variable flags[3].

Var.Break.Set flags[3] /Write /TraceEnable

```

**TraceEnable** can be used for high precision time-distance measurements:

```

;Get start and end address of function to be measured

&a1=sYmbol.BEGIN(func_to_measure)

&a2=sYmbol.EXIT(func_to_measure)

;Only generate trace messages on the addresses used for measurement

Break.Set &a1 /Program /TraceEnable

Break.Set &a2 /Program /TraceEnable

;run application

Trace.Init

Go

WAIT 5.s

Break

;statistic analysis

Trace.STATistic.AddressDURation &a1 &a2

;plot time distance over time (can take some time for analysis)

Trace.PROFILECHART.DURATION /FILTERA ADDRess &a1 /FILTERB ADDRess &a2

```

**NOTE:** The analysis commands can also be used without TraceEnable breakpoints, but the measurement will be less precise.

## Example: Event Controlled Program/Data Trace Start and End

Program and data trace can be enabled and disabled based on debug events. TraceON and TraceOFF control both program and data trace depending on **NEXUS.BTM** / **NEXUS.DTM** setting. TraceON and TraceOFF control the message source, i.e. the core's NEXUS module:

```

;Enable program/data trace when func2 is entered

;Disable program/data trace when last instruction of func2 is executed.

Break.Set sYmbol.BEGIN(func2) /Program /TraceON

Break.Set sYmbol.EXIT(func2) /Program /TraceOFF

```

```

;Enable program/data trace when variable flags[3] is written

Var.Break.Set flags[3] /Write /TraceON

;Disable program/data trace data when 16-bit value 0x1122 is

;written to address 0x40000230

Break.Set 0x40000230 /Write /Data.Word 0x1122 /TraceOFF

```

```

;Enable program/data trace only when a specific task is active

;NOTE: RTOS support must be set up correctly

&magic=0x40001280      ;set &magic to the task of interest

Break.Set task.config(magic) /Write /Data &magic /TraceON

Break.Set task.config(magic) /Write /Data !&magic /TraceOFF

```

It is also possible to enable/disable program and data trace messaging separately:

```

;Enable/disable only program trace based on events,

;full data trace messaging

NEXUS.DTM ReadWrite

Break.Set func2 /Program /Onchip /Alpha

TrOnchip.Alpha ProgramTraceON

Var.Break.Set flags[8] /Read /Onchip /Beta

TrOnchip.Beta ProgramTraceOFF

```

```

;In addition to full program trace, enable/disable data trace messaging

;only for func2

NEXUS.BTM ON

Break.Set SYmbol.BEGIN(func2) /Program /Onchip /Alpha

TrOnchip.Alpha DataTraceON

Break.Set SYmbol.EXIT(func2) /Program /Onchip /Beta

TrOnchip.Beta DataTraceOFF

```

## **Example: Event Controlled Trace Recording**

Debug/trace events can also be used to trigger and stop the trace recording (i.e. message sink):

```

;Generate a trigger for the trace recording module when

;the specified event occurs. Trace recording stops delayed after

;another 10% of the trace buffer size was recorded.

;

Break.Set sieve /Program /TraceTrigger

Trace.TDelay 10%

```

## **Example: Event Controlled Trigger Signals**

TRACE32 can generate a trigger signal based on debug/trace events. The trigger signal can be used to control PowerProbe or PowerIntegrator, as well as with external tools (using the trigger connector)

```

;Generate PODBUS trigger signal on data write event with data value

Var.Break.Set flags[9] /Write /Data.Byte 0x01 /BusTrigger

;forward signal to trigger connector

TrBus.Connect Out

TrBus.Mode High

```

## Example: Event Counter

---

There is also a built-in event counter which can be used to count debug/trace events or to measure the event frequency:

```

;Measure the execution frequency of function sieve

Break.Set sieve /Program /BusCount

Count.Mode Frequency

Count.Gate 1.s           ;measure for 1 second

Go                      ;run application

Count.Go                ;start measurement

PRINT "sieve freq = "+FORMAT.DECIMAL(1.,Count.VALUE()/1000.)+"Hz"

Count.state              ;open event counter window

```

## Tracing Peripheral Modules / Bus Masters

---

Many processors support tracing of peripheral bus master trace clients, e.g. DMA or GlobalRam controllers. The clients are controlled with the **NEXUS.CLIENT<x>** commands.

As for the core's data trace, the amount of generated trace messages is usually too high to be sent through the trace port and the on-chip message FIFO will overflow.

The use of SFT software trace requires code instrumentation done by users or OS vendors. Dedicated assembler instructions (DBCP, DBTAG, DBPUSH) are added to the code. When executed by the CPU, program counter values, immediate data or general purpose register values are output. These messages can be stored to the On-chip trace buffer or can be transferred in real time to the debug box by use of the LPD4 debug port interface.

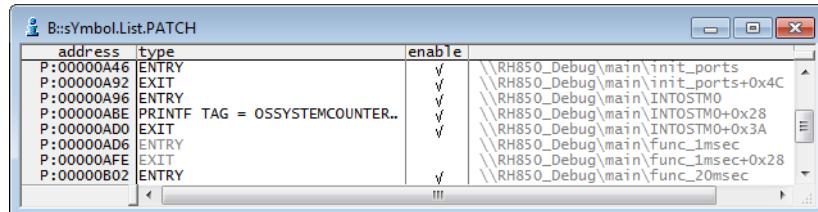

When using a GREENHILLS compiler, TRACE32 can extract all SFT-symbol information from the loaded ELF file. The symbol information can be displayed with command **sYmbol.List.PATCH**.

| address      | type                           | enable |                                      |

|--------------|--------------------------------|--------|--------------------------------------|

| P:000000A46  | ENTRY                          | ✓      | \\RH850_Debug\\main\\init_ports      |

| P:000000A92  | EXIT                           | ✓      | \\RH850_Debug\\main\\init_ports+0x4C |

| P:000000A96  | ENTRY                          | ✓      | \\RH850_Debug\\main\\INTOSTMO        |

| P:000000ABE  | PRINTF TAG = OSSYSTEMCOUNTER.. | ✓      | \\RH850_Debug\\main\\INTOSTMO+0x28   |

| P:000000A0D0 | EXIT                           | ✓      | \\RH850_Debug\\main\\INTOSTMO+0x3A   |

| P:000000A0D6 | ENTRY                          |        | \\RH850_Debug\\main\\func_1msec      |

| P:000000AFE  | EXIT                           |        | \\RH850_Debug\\main\\func_1msec+0x28 |

| P:000000B02  | ENTRY                          | ✓      | \\RH850_Debug\\main\\func_20msec     |

The “enable” row shows the status of the SFT code instrumentation. If there is a checkmark the instrumentation code is active, if there is none the original instrumentation code is patched by NOP instructions and no SFT message is generated. A simple mouse-click to the checkmark enables/disables the instrumentation code.

## SFT Software Trace to On-chip Trace

---