# CEVA-X Debugger and Trace

MANUAL

# CEVA-X Debugger and Trace

---

[TRACE32 Online Help](#)

[TRACE32 Directory](#)

[TRACE32 Index](#)

[TRACE32 Documents](#) .....

[ICD In-Circuit Debugger](#) .....

[Processor Architecture Manuals](#) .....

[CEVA-X](#) .....

**CEVA-X Debugger and Trace** .....

1

**Introduction** .....

5

Brief Overview of Documents for New Users

5

Demo and Start-up Scripts

5

**Warning** .....

6

**Quick Start** .....

7

**Troubleshooting** .....

9

**FAQ** .....

9

**CPU Specific Implementations** .....

10

Breakpoints

10

Software Breakpoints

10

On-chip Breakpoints

10

Disassembler

11

MS Windows

11

Linux

11

**CPU specific SYStem Settings** .....

12

SYStem.CONFIG.state

Display target configuration

12

SYStem.CONFIG

Configure debugger according to target topology

14

<parameters> describing the “DebugPort”

18

<parameters> describing the “JTAG” scan chain and signal behavior

20

<parameters> describing a system level TAP “MultiTap”

22

<parameters> configuring a CoreSight Debug Access Port “AP”

23

<parameters> describing debug and trace “Components”

29

<parameters> which are “Deprecated”

38

SYStem.CONFIG.EXTMEM

External program memory

40

SYStem.CPU

Select the used CPU

41

SYStem.JtagClock

Define JTAG clock

41

SYStem.LOCK

Lock and tristate the debug port

41

|                                            |                                               |           |

|--------------------------------------------|-----------------------------------------------|-----------|

| SYStem.MemAccess                           | Select run-time memory access method          | 42        |

| SYStem.Mode                                | Establish the communication with the target   | 42        |

| SYStem.Option.IMASKASM                     | Disable interrupts while single stepping      | 43        |

| SYStem.Option.IMASKHLL                     | Disable interrupts while HLL single stepping  | 44        |

| SYStem.Option.OVERLAY                      | Enable overlay support                        | 44        |

| SYStem.Option.PB0size                      | Setup size of internal program memory         | 45        |

| SYStem.Option.RisingTDO                    | Target outputs TDO on rising edge             | 45        |

| SYStem.VCU                                 | Vector Computation Units (VCU)                | 46        |

| SYStem.VCU.INSTances                       | Number of available VCUs                      | 46        |

| SYStem.VCU.MLD                             | MLD available or not                          | 46        |

| General Restrictions                       |                                               | 46        |

| <b>CEVA-X specific ETM Command</b>         |                                               | <b>47</b> |

| ETM.BranchBBC                              | Control branch BBC mode                       | 47        |

| ETM.IgnoreISyncPredicate                   | Ignore I-Sync predicates                      | 47        |

| ETM.LoopBBC                                | Branch broadcast                              | 47        |

| ETM.PredicateAddress                       | Set predicate address                         | 47        |

| ETM.PredicatePeriod                        | Predicated counter in ETM wrapper             | 48        |

| ETM.TimeStampInjectorTraceID               | CoreSight ATB ID                              | 48        |

| ETM.WrapperFilter                          | Global breakpoint enable                      | 48        |

| ETM.WrapperSTALL                           | Enable/disable wrapper stall                  | 48        |

| <b>TrOnchip Commands</b>                   |                                               | <b>49</b> |

| TrOnchip.CONVert                           | Adjust range breakpoint in on-chip resource   | 49        |

| TrOnchip.VarCONVert                        | Adjust complex breakpoint in on-chip resource | 49        |

| TrOnchip.RESet                             | Set on-chip trigger to default state          | 50        |

| TrOnchip.Set                               | Set breakpoint                                | 50        |

| TrOnchip.state                             | Display “Trigger-Onchip” dialog               | 50        |

| <b>Ceva Specific Benchmarking Commands</b> |                                               | <b>51</b> |

| BMC.CLOCKS.FORMAT                          | Cycle counter value format                    | 54        |

| <b>Memory Classes</b>                      |                                               | <b>55</b> |

| <b>JTAG Connector</b>                      |                                               | <b>56</b> |

# Introduction

---

Please keep in mind that only the **Processor Architecture Manual** (the document you are reading at the moment) is CPU specific, while all other parts of the online help are generic for all CPUs supported by Lauterbach. So if there are questions related to the CPU, the Processor Architecture Manual should be your first choice.

## Brief Overview of Documents for New Users

---

### Architecture-independent information:

- **“Training Basic Debugging”** (training\_debugger.pdf): Get familiar with the basic features of a TRACE32 debugger.

- **“T32Start”** (app\_t32start.pdf): T32Start assists you in starting TRACE32 PowerView instances for different configurations of the debugger. T32Start is only available for Windows.

- **“General Commands”** (general\_ref\_<x>.pdf): Alphabetic list of debug commands.

### Architecture-specific information:

- **“Processor Architecture Manuals”**: These manuals describe commands that are specific for the processor architecture supported by your Debug Cable. To access the manual for your processor architecture, proceed as follows:

- Choose **Help** menu > **Processor Architecture Manual**.

- **“OS Awareness Manuals”** (rtos\_<os>.pdf): TRACE32 PowerView can be extended for operating system-aware debugging. The appropriate OS Awareness manual informs you how to enable the OS-aware debugging.

## Demo and Start-up Scripts

---

Lauterbach provides ready-to-run start-up scripts for known CEVA-X based hardware.

### To search for PRACTICE scripts, do one of the following in TRACE32 PowerView:

- Type at the command line: **WELCOME.SCRIPTS**

- or choose **File** menu > **Search for Script**.

You can now search the demo folder and its subdirectories for PRACTICE start-up scripts (\*.cmm) and other demo software.

You can also manually navigate in the `~/demo/cevax/` subfolder of the system directory of TRACE32.

|                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>WARNING:</b> | <p>To prevent debugger and target from damage it is recommended to connect or disconnect the Debug Cable only while the target power is OFF.</p> <p>Recommendation for the software start:</p> <ol style="list-style-type: none"><li>1. Disconnect the Debug Cable from the target while the target power is off.</li><li>2. Connect the host system, the TRACE32 hardware and the Debug Cable.</li><li>3. Power ON the TRACE32 hardware.</li><li>4. Start the TRACE32 software to load the debugger firmware.</li><li>5. Connect the Debug Cable to the target.</li><li>6. Switch the target power ON.</li><li>7. Configure your debugger e.g. via a start-up script.</li></ol> <p>Power down:</p> <ol style="list-style-type: none"><li>1. Switch off the target power.</li><li>2. Disconnect the Debug Cable from the target.</li><li>3. Close the TRACE32 software.</li><li>4. Power OFF the TRACE32 hardware.</li></ol> |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

# Quick Start

---

Starting up the debugger is done as follows:

1. Select the device prompt for the ICD Debugger and reset the system.

```

B::

RESet

```

The device prompt `B::` is normally already selected in the command line. If this is not the case, enter `B::` to set the correct device prompt. The `RESet` command is only necessary if you do not start directly after booting the TRACE32 development tool.

2. Specify the CPU.

```

SYStem.CPU <cpu_type>

```

The default values of all other options are set in such a way that it should be possible to work without modification. Please consider that this is probably not the best configuration for your target.

3. Set the JTAG frequency

```

SYStem.JtagClock <frequency>

```

The default value is 1.0 MHz.

4. Inform the debugger about read-only address ranges (ROM, FLASH).

```

MAP.BOnchip <range>

```

The B(reak)Onchip information is necessary to decide where on-chip breakpoints must be used. On-chip breakpoints are necessary to set program breakpoints to FLASH/ROM. The sections of FLASH and ROM depend on the specific CPU and its chip selects.

5. Enter debug mode.

```

SYStem.Up

```

This command resets the CPU and enters debug mode. After this command is executed it is possible to access memory and registers.

## 6. Load the program.

```

Data.LOAD.COFF program.a      ; COFF specifies the format, program.a

; is the file name)

```

The format of the **Data.LOAD** command depends on the file format generated by the compiler.

A detailed description of the **Data.LOAD** command and all available options is given in the "[General Reference Guide](#)".

A typical start sequence for the TeakLiteDev-C is shown below. This sequence can be written to a PRACTICE script file (\*.cmm, ASCII format) and executed with the command **DO <file>**. Other sequences can be found in the `~/demo/` directory.

```

B:::                                ; Select the ICD device prompt

WinClear                         ; Clear all windows

SYS.CPU TeakLiteDev-C           ; Select CPU

SYStem.JtagClock 10MHz          ; Choose JTAG frequency

SYStem.UP                         ; Reset the target and enter debug mode

Data.LOAD.COFF demo.a           ; Load the application with option large

; memory model and verify the process

Register.Set PC start           ; Set program counter

List.Mix                          ; Open source code window      *)

Go main                           ; Run and break at main()

Register.view /SpotLight         ; Open register window        *)

Var.Local                         ; Open window with local variables *)

```

\*) These commands open windows on the screen. The window position can be specified with the [WinPOS](#) command.

# Troubleshooting

---

No information available

# FAQ

---

Please refer to <https://support.lauterbach.com/kb>.

## Breakpoints

---

There are two types of breakpoints available: Software breakpoints and on-chip breakpoints.

## Software Breakpoints

---

Software breakpoints are the default breakpoints for program breakpoints. A software breakpoint is implemented by patching a break code into the memory.

There is no restriction in the number of software breakpoints.

## On-chip Breakpoints

---

The resources for the on-chip breakpoints are provided by the CPU.

The following list gives an overview of the supported on-chip breakpoints:

- **On-chip breakpoints:** Total amount of available on-chip breakpoints.

- **Instruction breakpoints:** Number of on-chip breakpoints that can be used to set Program breakpoints into ROM/FLASH/EEPROM.

- **Read/Write breakpoints:** Number of on-chip breakpoints that can be used as Read or Write breakpoints.

- **Data breakpoint:** Number of on-chip data breakpoints that can be used to stop the program when a specific data value is written to an address or when a specific data value is read from an address.

| Family | Onchip Breakpoints            | Program Breakpoints | Read/Write Breakpoints    | Data Value Breakpoints |

|--------|-------------------------------|---------------------|---------------------------|------------------------|

| CEVA-X | 4 instruction<br>4 read/write | 4 single address    | 4 single address or range | 2                      |

Starting with CEVA-ToolBox v18, TRACE32 must be configured to use the disassembler libraries provided by Ceva. The only exception from this rule is the NeuPro (Ceva-XM6), which can optionally still use the build-in disassembler of TRACE32.

## MS Windows

---

1. Install CEVA-ToolBox for your CPU.

2. Browse to <CEVA-ToolBox>\<version>\<cpu>\cevatoools\bin.

3. Copy the following two files to <TRACE32>\bin\windows64:

- cevaxasmsrv.dll

- <cpu>db.dll

4. Add the following line to your \*.cmm script:

```

apu.load ~~/bin/windows64/t32cevadislink.dll "cevaxasmsrv.dll" "<cpu>"

```

## Linux

---

1. Install CEVA-ToolBox for your CPU.

2. Optional: Browse to <CEVA-ToolBox>/<version>/<cpu>/cevatoools/bin.

3. Optional: Copy the following two files to <TRACE32>/bin/pc\_linux64:

- libcevaxasmsrv.so

- lib<cpu>db.so

4. Add the path of the disassembler libraries (step 2 or step 3) to LD\_LIBRARY\_PATH:

```

export LD_LIBRARY_PATH=<path_to_libraries>

```

5. Add the following line to your \*.cmm script:

```

apu.load ~~/bin/pc_linux64/t32cevadislink.so "libcevaxasmsrv.so" "<cpu>"

```

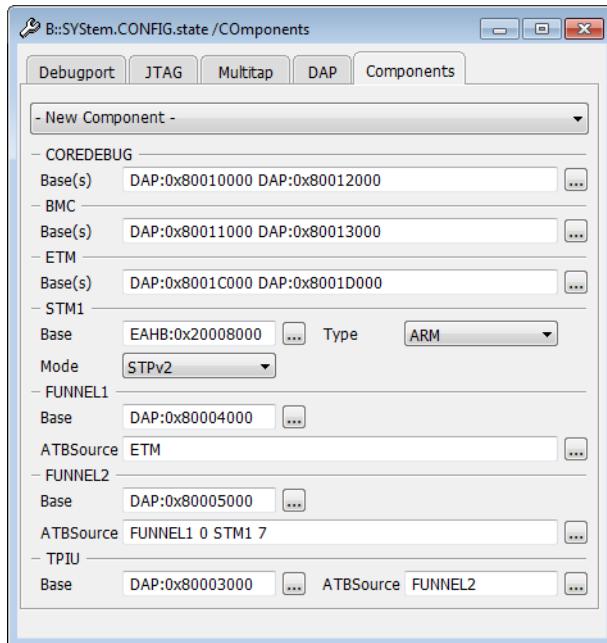

## SYStem.CONFIG.state

Display target configuration

Format: **SYStem.CONFIG.state [/<tab>]**

<tab>: **DebugPort | Jtag | AccessPorts | COnponents**

Opens the **SYStem.CONFIG.state** window, where you can view and modify most of the target configuration settings. The configuration settings tell the debugger how to communicate with the chip on the target board and how to access the on-chip debug and trace facilities in order to accomplish the debugger's operations.

Alternatively, you can modify the target configuration settings via the [TRACE32 command line](#) with the **SYStem.CONFIG** commands. Note that the command line provides *additional* **SYStem.CONFIG** commands for settings that are *not* included in the **SYStem.CONFIG.state** window.

|                               |                                                                                                                                                                                                                                                                                                            |

|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <tab>                         | Opens the <b>SYStem.CONFIG.state</b> window on the specified tab. For tab descriptions, see below.                                                                                                                                                                                                         |

| <b>DebugPort</b><br>(default) | The <b>DebugPort</b> tab informs the debugger about the debug connector type and the communication protocol it shall use.<br><br>For descriptions of the commands on the <b>DebugPort</b> tab, see <a href="#">DebugPort</a> .                                                                             |

| <b>Jtag</b>                   | The <b>Jtag</b> tab informs the debugger about the position of the Test Access Ports (TAP) in the JTAG chain which the debugger needs to talk to in order to access the debug and trace facilities on the chip.<br><br>For descriptions of the commands on the <b>Jtag</b> tab, see <a href="#">Jtag</a> . |

| <b>AccessPorts</b>            | This tab informs the debugger about an Arm CoreSight Access Port (AP) and about how to control the AP to access chip-internal memory busses (AHB, APB, AXI) or chip-internal JTAG interfaces.<br><br>For a descriptions of a corresponding commands, refer to <a href="#">AP</a> .                         |

|                    |                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>CComponents</b> | <p>The <b>CComponents</b> tab informs the debugger (a) about the existence and interconnection of on-chip CoreSight debug and trace modules and (b) informs the debugger on which memory bus and at which base address the debugger can find the control registers of the modules.</p> <p>For descriptions of the commands on the <b>CComponents</b> tab, see <a href="#">CComponents</a>.</p> |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                            |                                                                                                                                                                                                                                                                                                                                      |

|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Format:                                    | <b>SYStem.CONFIG</b> <parameter><br><b>SYStem.MultiCore</b> <parameter> (deprecated)                                                                                                                                                                                                                                                 |

| <parameter>:<br><b>(DebugPort)</b>         | <b>CONNECTOR</b> [MIPI34   MIPI20T]<br><b>CORE</b> <core> <chip><br><b>DEBUGPORT</b> [DebugCable0   DebugCableA   DebugCableB]<br><b>DEBUGPORTTYPE</b> [JTAG   SWD   CJTAG]<br><br><b>Slave</b> [ON   OFF]<br><b>SWDP</b> [ON   OFF]<br><b>SWDPIDLEHIGH</b> [ON   OFF]<br><b>SWDPTargetSel</b> <value><br><b>TriState</b> [ON   OFF] |

| <parameter>:<br><b>(JTAG)</b>              | <b>DAPDRPOST</b> <bits><br><b>DAPDRPRE</b> <bits><br><b>DAPIRPOST</b> <bits><br><b>DAPIRPRE</b> <bits><br><br><b>DRPOST</b> <bits><br><b>DRPRE</b> <bits><br><b>IRPOST</b> <bits><br><b>IRPRE</b> <bits><br><br><b>Slave</b> [ON   OFF]<br><b>TAPState</b> <state><br><b>TCKLevel</b> <level><br><b>TriState</b> [ON   OFF]          |

| <parameter>:<br><b>(MultiTap)</b>          | <b>CFGCONNECT</b> <code><br><b>MULTITAP</b> [NONE   IcepickA   IcepickB   IcepickC   IcepickD   IcepickBB   IcepickBC   IcepickCC   IcepickDD   STCLTAP1   STCLTAP2   STCLTAP3  <br><b>MSMTAP</b> <irlength> <irvalue> <drlength> <drvvalue><br><b>JtagSEQUence</b> <sub_cmd>]                                                       |

| <parameter>:<br><b>(AccessPorts</b><br><>) | <b>AHBAPn.Base</b> <address><br><b>AHBAPn.HPROT</b> [<value>   <name>]<br><b>AHBAPn.Port</b> <port><br><b>AHBAPn.RESet</b><br><b>AHBAPn.view</b><br><b>AHBAPn.XtorName</b> <name><br><br><b>APBAPn.Base</b> <address><br><b>APBAPn.Port</b> <port>                                                                                   |

|                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <p><b>&lt;parameter&gt;:</b><br/> <b>(AccessPorts</b><br/> <b>cont.)</b></p> | <p><b>APBAPn.RESet</b><br/> <b>APBAPn.view</b><br/> <b>APBAPn.XtorName &lt;name&gt;</b></p> <p><b>AXIAPn.ACCEnable [ON   OFF]</b><br/> <b>AXIAPn.Base &lt;address&gt;</b><br/> <b>AXIAPn.CacheFlags &lt;value&gt;</b><br/> <b>AXIAPn.HPROT [&lt;value&gt;   &lt;name&gt;]</b><br/> <b>AXIAPn.Port &lt;port&gt;</b><br/> <b>AXIAPn.RESet</b><br/> <b>AXIAPn.view</b><br/> <b>AXIAPn.XtorName &lt;name&gt;</b></p> <p><b>DEBUGAPn.Port &lt;port&gt;</b><br/> <b>DEBUGAPn.RESet</b><br/> <b>DEBUGAPn.view</b><br/> <b>DEBUGAPn.XtorName &lt;name&gt;</b></p> <p><b>JTAGAPn.Base &lt;address&gt;</b><br/> <b>JTAGAPn.Port &lt;port&gt;</b><br/> <b>JTAGAPn.CorePort &lt;port&gt;</b><br/> <b>JTAGAPn.RESet</b><br/> <b>JTAGAPn.view</b><br/> <b>JTAGAPn.XtorName &lt;name&gt;</b></p> <p><b>MEMORYAPn.HPROT [&lt;value&gt;   &lt;name&gt;]</b><br/> <b>MEMORYAPn.Port &lt;port&gt;</b><br/> <b>MEMORYAPn.RESet</b><br/> <b>MEMORYAPn.view</b><br/> <b>MEMORYAPn.XtorName &lt;name&gt;</b></p> |

| <p><b>&lt;parameter&gt;:</b><br/> <b>(CComponents)</b></p>                   | <p><b>COREDEBUG.Base &lt;address&gt;</b><br/> <b>COREDEBUG.RESet</b><br/> <b>COREDEBUG.view</b></p> <p><b>CTI.Base &lt;address&gt;</b><br/> <b>CTI.Config [NONE   ARMV1   ARMPostInit   OMAP3   TMS570   CortexV1   QV1]</b><br/> <b>CTI.RESet</b><br/> <b>CTI.view</b></p> <p><b>ETB.ATBSource &lt;source&gt;</b><br/> <b>ETB.Base &lt;address&gt;</b><br/> <b>ETB.Name &lt;string&gt;</b><br/> <b>ETB.NoFlush [ON   OFF]</b><br/> <b>ETB.RESet</b><br/> <b>ETB.Size &lt;size&gt;</b><br/> <b>ETB.SStackMode [NotAvailbale   TRGETM   FULLTIDRM   NOTSET   FULLSTOP   FULLCTI]</b><br/> <b>ETB.view</b></p>                                                                                                                                                                                                                                                                                                                                                                              |

**<parameter>:**

(COmponents

cont.)

**ETF.ATBSource <source>**

**ETF.Base <address>**

**ETF.Name <string>**

**ETF.NoFlush [ON | OFF]**

**ETF.RESet**

**ETF.Size <size>**

**ETF.SStackMode [NotAvailbale | TRGETM | FULLTIDRM | NOTSET | FULLSTOP | FULLCTI]**

**ETF.view**

**ETM.Base <address>**

**ETM.RESet**

**ETM.view**

**ETR.ATBSource <source>**

**ETR.Base <address>**

**ETR.CATUBase <address>**

**ETR.Name <string>**

**ETR.NoFlush [ON | OFF]**

**ETR.RESet**

**ETR.Size <size>**

**ETR.SStackMode [NotAvailbale | TRGETM | FULLTIDRM | NOTSET | FULLSTOP | FULLCTI]**

**ETR.view**

**ETS.ATBSource <source>**

**ETS.Base <address>**

**ETS.Name <string>**

**ETS.NoFlush [ON | OFF]**

**ETS.RESet**

**ETS.Size <size>**

**ETS.SStackMode [NotAvailbale | TRGETM | FULLTIDRM | NOTSET | FULLSTOP | FULLCTI]**

**ETS.view**

**FUNNEL.ATBSource <sourcelist>**

**FUNNEL.Base <address>**

**FUNNEL.Name <string>**

**FUNNEL.PROGrammable [ON | OFF]**

**FUNNEL.view**

**FUNNEL.RESet**

**HTM.Base <address>**

**HTM.RESet**

**HTM.Type [CoreSight | WPT]**

**REP.ATBSource <source>**

**REP.Base <address>**

**REP.Name <string>**

**REP.RESet**

**REP.view**

**STM.Base <address>**

**STM.Mode [NONE | XTIv2 | SDTI | STP | STP64 | STPv2]**

**STM.RESet**

**STM.Type [None | GenericARM | SDTI | TI]**

```

<parameter>:          COREBASE <address>

(Deprecated)          CTIBASE <address>

CTICONFIG [NONE | ARMV1 | ARMPostInit | OMAP3 | TMS570 | CortexV1 |

QV1]

DEBUGBASE <address>

ETBBASE <address>

ETBFUNNELBASE <address>

ETFBASE <address>

ETMBASE <address>

ETMETBFUNNELPORT <port>

ETMFUNNEL2PORT <port>

ETMFUNNELPORT <port>

ETMTPUIFUNNELPORT <port>

FUNNEL2BASE <address>

FUNNELBASE <address>

HTMBASE <address>

HTMETBFUNNELPORT <port>

HTMFUNNEL2PORT <port>

HTMFUNNELPORT <port>

HTMTPUIFUNNELPORT <port>

TPIUBASE <address>

TPIUFUNNELBASE <address>

view

AHBACCESSPORT <port>

APBACCESSPORT <port>

AXIACCESSPORT <port>

COREJTAGPORT <port>

DEBUGACCESSPORT <port>

JTAGACCESSPORT <port>

MEMORYACCESSPORT <port>

```

The **SYStem.CONFIG** commands inform the debugger about the available on-chip debug and trace components and how to access them.

Some commands need a certain CPU type selection (**SYStem.CPU <type>**) to become active and might additionally depend on further settings.

Ideally you can select with **SYStem.CPU** the chip you are using which causes all setup you need and you do not need any further **SYStem.CONFIG** command.

The **SYStem.CONFIG** command information shall be provided after the **SYStem.CPU** command, which might be a precondition to enter certain **SYStem.CONFIG** commands, and before you start up the debug session e.g. by **SYStem.Up**.

**CONNECTOR

[MIPI34 | MIPI20T]**

Specifies the connector “MIPI34” or “MIPI20T” on the target. This is mainly needed in order to notify the trace pin location.

Default: MIPI34 if CombiProbe is used.

**CORE <core> <chip>**

The command helps to identify debug and trace resources which are commonly used by different cores. The command might be required in a multicore environment if you use multiple debugger instances (multiple TRACE32 PowerView GUIs) to simultaneously debug different cores on the same target system.

Because of the default setting of this command

```

debugger#1: <core>=1 <chip>=1

debugger#2: <core>=1 <chip>=2

...

```

each debugger instance assumes that all notified debug and trace resources can exclusively be used.

But some target systems have shared resources for different cores, for example a common trace port. The default setting causes that each debugger instance controls the same trace port. Sometimes it does not hurt if such a module is controlled twice. But sometimes it is a must to tell the debugger that these cores share resources on the same <chip>. Whereby the “chip” does not need to be identical with the device on your target board:

```

debugger#1: <core>=1 <chip>=1

debugger#2: <core>=2 <chip>=1

```

**CORE <core> <chip>**

(cont.)

For cores on the same <chip>, the debugger assumes that the cores share the same resource if the control registers of the resource have the same address.

Default:

<core> depends on CPU selection, usually 1.

<chip> derived from CORE= parameter in the configuration file (config.t32), usually 1. If you start multiple debugger instances with the help of t32start.exe, you will get ascending values (1, 2, 3,...).

**DEBUGPORT

[DebugCable0 | DebugCableA | DebugCableB]**

It specifies which probe cable shall be used e.g. “DebugCableA” or “DebugCableB”. At the moment only the CombiProbe allows to connect more than one probe cable.

Default: depends on detection.

|                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>DEBUGPORTTYPE</b><br>[JTAG   SWD   CJTAG  <br>CJTAGSWD] | It specifies the used debug port type “JTAG”, “SWD”, “CJTAG”, “CJTAG-SWD”. It assumes the selected type is supported by the target.                                                                                                                                                                                                                                                                                                                            |

|                                                            | Default: JTAG.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| <b>Slave</b> [ON   OFF]                                    | If several debuggers share the same debug port, all except one must have this option active.<br><br>JTAG: Only one debugger - the “master” - is allowed to control the signals nTRST and nSRST (nRESET). The other debuggers need to have the setting <b>Slave ON</b> .                                                                                                                                                                                        |

|                                                            | Default: OFF.<br>Default: ON if CORE=... >1 in the configuration file (e.g. config.t32).                                                                                                                                                                                                                                                                                                                                                                       |

| <b>SWDPIidleHigh</b><br>[ON   OFF]                         | Keep SWDIO line high when idle. Only for Serialwire Debug mode. Usually the debugger will pull the SWDIO data line low, when no operation is in progress, so while the clock on the SWCLK line is stopped (kept low).<br><br>You can configure the debugger to pull the SWDIO data line high, when no operation is in progress by using<br><b>SYStem.CONFIG SWDPIidleHigh ON</b>                                                                               |

|                                                            | Default: OFF.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| <b>SWDPTargetSel</b> <value>                               | Device address in case of a multidrop serial wire debug port.<br><br>Default: none set (any address accepted).                                                                                                                                                                                                                                                                                                                                                 |

| <b>TriState</b> [ON   OFF]                                 | TriState has to be used if several debug cables are connected to a common JTAG port. TAPState and TCKLevel define the TAP state and TCK level which is selected when the debugger switches to tristate mode.<br><br>Please note: <ul style="list-style-type: none"><li>• nTRST must have a pull-up resistor on the target.</li><li>• TCK can have a pull-up or pull-down resistor.</li><li>• Other trigger inputs need to be kept in inactive state.</li></ul> |

|                                                            | Default: OFF.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

With the JTAG interface you can access a Test Access Port controller (TAP) which has implemented a state machine to provide a mechanism to read and write data to an Instruction Register (IR) and a Data Register (DR) in the TAP. The JTAG interface will be controlled by 5 signals:

- nTRST (reset)

- TCK (clock)

- TMS (state machine control)

- TDI (data input)

- TDO (data output)

Multiple TAPs can be controlled by one JTAG interface by daisy-chaining the TAPs (serial connection). If you want to talk to one TAP in the chain, you need to send a BYPASS pattern (all ones) to all other TAPs. For this case the debugger needs to know the position of the TAP it wants to talk to. The TAP position can be defined with the first four commands in the table below.

|                          |                                                                                                                                                                                                                                                                 |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ... <b>DRPOST</b> <bits> | Defines the TAP position in a JTAG scan chain. Number of TAPs in the JTAG chain between the TDI signal and the TAP you are describing. In BYPASS mode, each TAP contributes one data register bit. See possible TAP types and example below.<br><br>Default: 0. |

| ... <b>DRPRE</b> <bits>  | Defines the TAP position in a JTAG scan chain. Number of TAPs in the JTAG chain between the TAP you are describing and the TDO signal. In BYPASS mode, each TAP contributes one data register bit. See possible TAP types and example below.<br><br>Default: 0. |

| ... <b>IRPOST</b> <bits> | Defines the TAP position in a JTAG scan chain. Number of Instruction Register (IR) bits of all TAPs in the JTAG chain between TDI signal and the TAP you are describing. See possible TAP types and example below.<br><br>Default: 0.                           |

| ... <b>IRPRE</b> <bits>  | Defines the TAP position in a JTAG scan chain. Number of Instruction Register (IR) bits of all TAPs in the JTAG chain between the TAP you are describing and the TDO signal. See possible TAP types and example below.<br><br>Default: 0.                       |

**NOTE:** If you are not sure about your settings concerning **IRPRE**, **IRPOST**, **DRPRE**, and **DRPOST**, you can try to detect the settings automatically with the **SYStem.DETECT.DaisyChain** command.

|                                |                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Slave [ON   OFF]</b>        | If several debuggers share the same debug port, all except one must have this option active.<br><br>JTAG: Only one debugger - the “master” - is allowed to control the signals nTRST and nSRST (nRESET). The other debuggers need to have the setting <b>Slave OFF</b> .<br><br>Default: OFF.<br>Default: ON if CORE=... >1 in the configuration file (e.g. config.t32).                                            |

| <b>TAPState &lt;state&gt;</b>  | This is the state of the TAP controller when the debugger switches to tristate mode. All states of the JTAG TAP controller are selectable.<br><br>0 Exit2-DR<br>1 Exit1-DR<br>2 Shift-DR<br>3 Pause-DR<br>4 Select-IR-Scan<br>5 Update-DR<br>6 Capture-DR<br>7 Select-DR-Scan<br>8 Exit2-IR<br>9 Exit1-IR<br>10 Shift-IR<br>11 Pause-IR<br>12 Run-Test/Idle<br>13 Update-IR<br>14 Capture-IR<br>15 Test-Logic-Reset |

|                                | Default: 7 = Select-DR-Scan.                                                                                                                                                                                                                                                                                                                                                                                        |

| <b>TCKLevel &lt;/level&gt;</b> | Level of TCK signal when all debuggers are tristated. Normally defined by a pull-up or pull-down resistor on the target.<br><br>Default: 0.                                                                                                                                                                                                                                                                         |

|                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>TriState [ON   OFF]</b> | TriState has to be used if several debug cables are connected to a common JTAG port. TAPState and TCKLevel define the TAP state and TCK level which is selected when the debugger switches to tristate mode.<br><br>Please note: <ul style="list-style-type: none"><li>• nTRST must have a pull-up resistor on the target.</li><li>• TCK can have a pull-up or pull-down resistor.</li><li>• Other trigger inputs need to be kept in inactive state.</li></ul> |

|                            | Default: OFF.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

## TAP types:

Core TAP providing access to the debug register of the core you intend to debug.

-> DRPOST, DRPRE, IRPOST, IRPRE.

DAP (Debug Access Port) TAP providing access to the debug register of the core you intend to debug. It might be needed additionally to a Core TAP if the DAP is only used to access memory and not to access the core debug register.

-> DAPDRPOST, DAPDRPRE, DAPIRPOST, DAPIRPRE.

## **<parameters> describing a system level TAP “MultiTap”**

---

A “Multitap” is a system level or chip level test access port (TAP) in a JTAG scan chain. It can for example provide functions to re-configure the JTAG chain or view and control power, clock, reset and security of different chip components.

### **CFGCONNECT <code>**

The *<code>* is a hexadecimal number which defines the JTAG scan chain configuration. You need the chip documentation to figure out the suitable code. In most cases the chip specific default value can be used for the debug session.

Used if MULTITAP=STCLTAPx.

### **MULTITAP**

[NONE | IcepickA | IcepickB

| IcepickC | IcepickD |

IcepickM |

IcepickBB | IcepickBC |

IcepickCC | IcepickDD |

STCLTAP1 | STCLTAP2 |

STCLTAP3 | MSMTAP

<irlength> <irvalue>

<drlength> <drvalue>

**JtagSEQuence <sub\_cmd>**]

Selects the type and version of the MULTITAP.

In case of MSMTAP you need to add parameters which specify which IR pattern and DR pattern needed to be shifted by the debugger to initialize the MSMTAP. Please note some of these parameters need a decimal input (dot at the end).

IcepickXY means that there is an Icepick version “X” which includes a subsystem with an Icepick of version “Y”.

For a description of the **JtagSEQuence** subcommands, see [SYStem.CONFIG.MULTITAP JtagSEQuence](#).

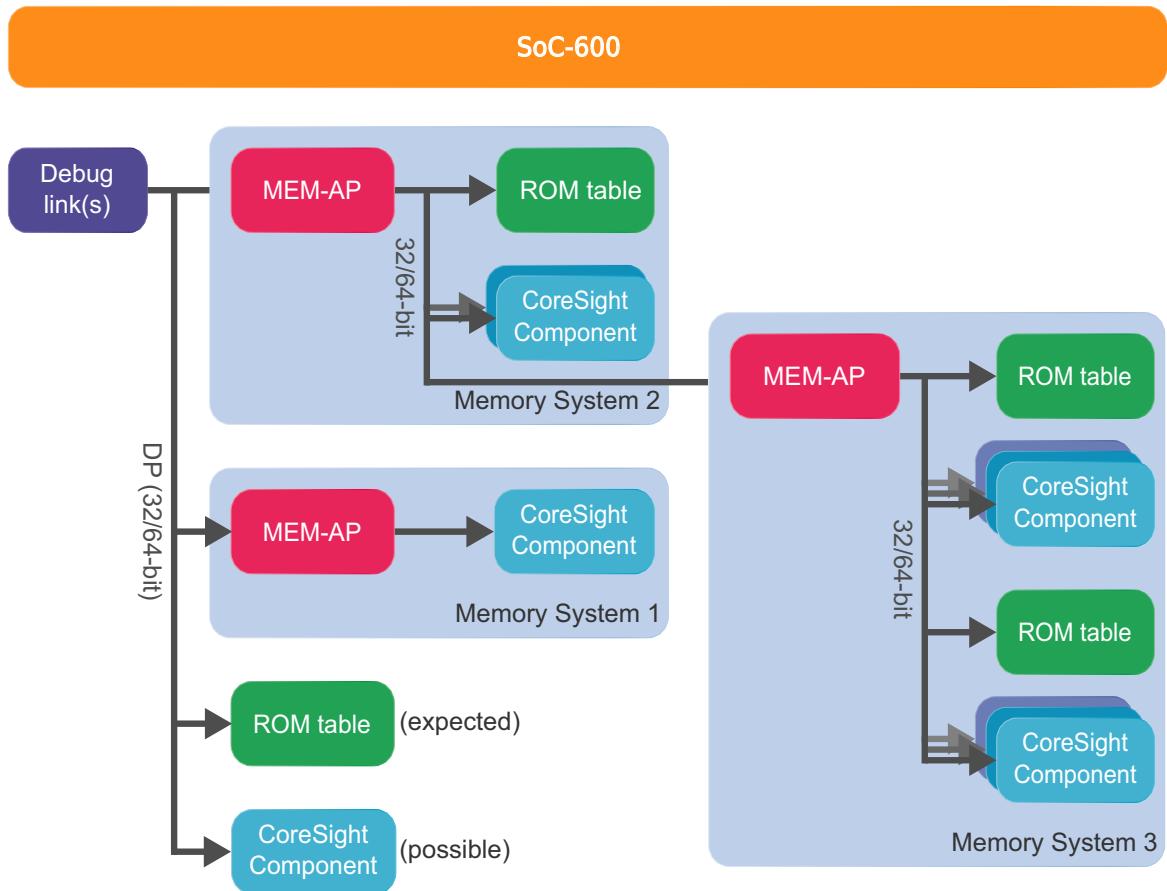

An Access Port (AP) is a CoreSight module from ARM which provides access via its debug link (JTAG, cJTAG, SWD, USB, UDP/TCP-IP, GTL, PCIe...) to:

1. Different memory busses (AHB, APB, AXI). This is especially important if the on-chip debug register needs to be accessed this way. You can access the memory buses by using certain access classes with the debugger commands: “AHB:”, “APB:”, “AXI:”, “DAP”, “E:”. The interface to these buses is called Memory Access Port (MEM-AP).

2. Other, chip-internal JTAG interfaces. This is especially important if the core you intend to debug is connected to such an internal JTAG interface. The module controlling these JTAG interfaces is called JTAG Access Port (JTAG-AP). Each JTAG-AP can control up to 8 internal JTAG interfaces. A port number between 0 and 7 denotes the JTAG interfaces to be addressed.

3. A transactor name for virtual connections to AMBA bus level transactors can be configured by the property **SYStem.CONFIG.\*APn.XtorName <name>**. A JTAG or SWD transactor must be configured for virtual connections to use the property “Port” or “Base” (with “DP:” access) in case XtorName remains empty.

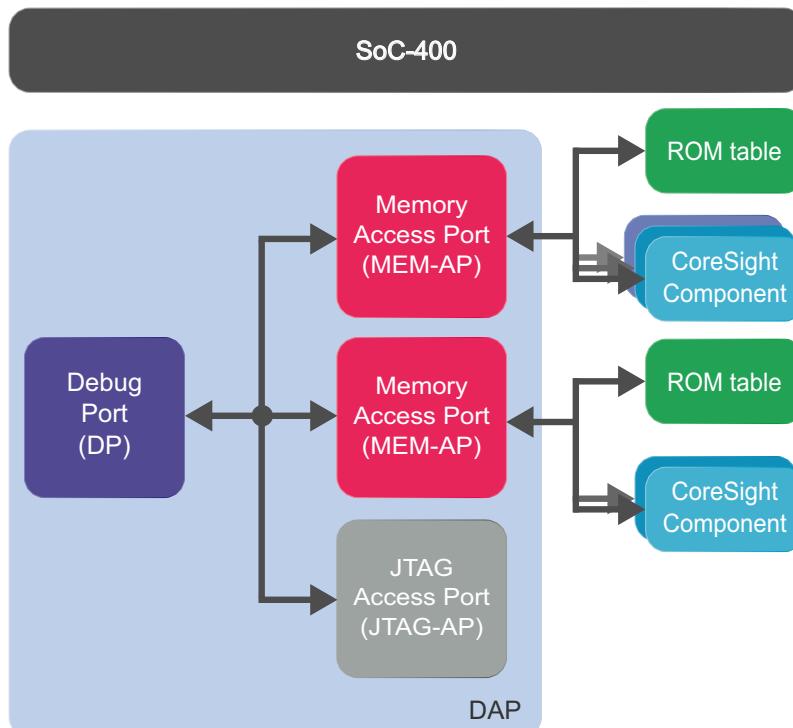

### Example 1: SoC-400

**AHBAPn.HPROT** [*<value>* | *<name>*]

Default: 0.

Selects the value used for the HPROT bits in the Control Status Word (CSW) of a CoreSight AHB Access Port, when using the AHB: memory class.

**AXIAPn.HPROT** [*<value>* | *<name>*]

Default: 0.

This option selects the value used for the HPROT bits in the Control Status Word (CSW) of a CoreSight AXI Access Port, when using the AXI: memory class.

**MEMORYAPn.HPROT** [*<value>* | *<name>*]

Default: 0.

This option selects the value used for the HPROT bits in the Control Status Word (CSW) of a CoreSight Memory Access Port, when using the E: memory class.

|                                                  |                                                                                                                                                                                                                                                      |

|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>AXIAPn.ACEEnable [ON   OFF]</b>               | Default: OFF.<br>Enables ACE transactions on the AXI-AP, including barriers. This does only work if the debug logic of the target CPU implements coherent accesses. Otherwise this option will be without effect.                                    |

| <b>AXIAPn.CacheFlags</b><br><i>&lt;value&gt;</i> | Default: DeviceSYStem (=0x30: Domain=0x3, Cache=0x0).<br>This option configures the value used for the Cache and Domain bits in the Control Status Word (CSW[27:24]->Cache, CSW[14:13]->Domain) of an Access Port, when using the AXI: memory class. |

The below offered selection options are all non-bufferable. Alternatively you can enter a *<value>*, where value[5:4] determines the Domain bits and value[3:0] the Cache bits.

| <i>&lt;name&gt;</i>                           | Description                                                          |

|-----------------------------------------------|----------------------------------------------------------------------|

| <b>DeviceSYStem</b>                           | =0x30: Domain=0x3, Cache=0x0                                         |

| <b>NonCacheableSYStem</b>                     | =0x32: Domain=0x3, Cache=0x2                                         |

| <b>ReadAllocateNonShareable</b>               | =0x06: Domain=0x0, Cache=0x6                                         |

| <b>ReadAllocateInnerShareable</b>             | =0x16: Domain=0x1, Cache=0x6                                         |

| <b>ReadAllocateOuterShareable</b>             | =0x26: Domain=0x2, Cache=0x6                                         |

| <b>WriteAllocateNonShareable</b>              | =0x0A: Domain=0x0, Cache=0xA                                         |

| <b>WriteAllocateInnerShareable</b>            | =0x1A: Domain=0x1, Cache=0xA                                         |

| <b>WriteAllocateOuterShareable</b>            | =0x2A: Domain=0x2, Cache=0xA                                         |

| <b>ReadWriteAllocateNonShareable</b>          | =0x0E: Domain=0x0, Cache=0xE                                         |

| <b>ReadWriteAllocateInnerShareable</b>        | =0x1E: Domain=0x1, Cache=0xE                                         |

| <b>ReadWriteAllocateOuterShareable</b>        | =0x2E: Domain=0x2, Cache=0xE                                         |

| <b>AHBAPn.XtorName</b><br><i>&lt;name&gt;</i> | AHB bus transactor name that shall be used for “AHBn:” access class. |

| <b>APBAPn.XtorName</b> <i>&lt;name&gt;</i>    | APB bus transactor name that shall be used for “APBn:” access class. |

**AXIAPn.XtorName** *<name>* AXI bus transactor name that shall be used for “AXIn:” access class.

**DEBUGAPn.XtorName** *<name>* APB bus transactor name identifying the bus where the debug register can be found. Used for “DAP:” access class.

**MEMORYAPn.XtorName** *<name>* AHB bus transactor name identifying the bus where system memory can be accessed even during runtime. Used for “E:” access class while running, assuming “**SYStem.MemAccess DAP**”.

**... .RESet** Undo the configuration for this access port. This does not cause a physical reset for the access port on the chip.

**... .view** Opens a window showing the current configuration of the access port.

|                                                                              |                                                                                                                                                                                                                                      |

|------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>AHBAPn.Port</b> <port><br><b>AHBACCESSPORT</b> <port><br>(deprecated)     | Access Port Number (0-255) of a SoC-400 system which shall be used for “AHBn:” access class. Default: <port>=0.                                                                                                                      |

| <b>APBAPn.Port</b> <port><br><b>APBACCESSPORT</b> <port><br>(deprecated)     | Access Port Number (0-255) of a SoC-400 system which shall be used for “APBn:” access class. Default: <port>=1.                                                                                                                      |

| <b>AXIAPn.Port</b> <port><br><b>AXIACCESSPORT</b> <port><br>(deprecated)     | Access Port Number (0-255) of a SoC-400 system which shall be used for “AXIn:” access class. Default: port not available.                                                                                                            |

| <b>DEBUGAPn.Port</b> <port><br><b>DEBUGACCESSPORT</b> <port> (deprecated)    | AP access port number (0-255) of a SoC-400 system where the debug register can be found (typically on APB). Used for “DAP:” access class. Default: <port>=1.                                                                         |

| <b>JTAGAPn.CorePort</b> <port><br><b>COREJTAGPORT</b> <port><br>(deprecated) | JTAG-AP port number (0-7) connected to the core which shall be debugged.                                                                                                                                                             |

| <b>JTAGAPn.Port</b> <port><br><b>JTAGACCESSPORT</b> <port><br>(deprecated)   | Access port number (0-255) of a SoC-400 system of the JTAG Access Port.                                                                                                                                                              |

| <b>MEMORYAPn.Port</b> <port><br><b>MEMORYACCESSPORT</b> <port> (deprecated)  | AP access port number (0-255) of a SoC-400 system where system memory can be accessed even during runtime (typically an AHB). Used for “E:” access class while running, assuming “ <b>SYStem.MemAccess DAP</b> ”. Default: <port>=0. |

**AHBAPn.Base <address>**

This command informs the debugger about the start address of the register block of the “AHBAPn:” access port. And this way it notifies the existence of the access port. An access port typically provides a control register block which needs to be accessed by the debugger to read/write from/to the bus connected to the access port.

**Example:** SYStem.CONFIG.AHBAP1.Base DP:0x80002000

Meaning: The control register block of the AHB access ports starts at address 0x80002000.

**APBAPn.Base <address>**

This command informs the debugger about the start address of the register block of the “APBAPn:” access port. And this way it notifies the existence of the access port. An access port typically provides a control register block which needs to be accessed by the debugger to read/write from/to the bus connected to the access port.

**Example:** SYStem.CONFIG.APBAP1.Base DP:0x80003000

Meaning: The control register block of the APB access ports starts at address 0x80003000.

**AXIAPn.Base <address>**

This command informs the debugger about the start address of the register block of the “AXIAPn:” access port. And this way it notifies the existence of the access port. An access port typically provides a control register block which needs to be accessed by the debugger to read/write from/to the bus connected to the access port.

**Example:** SYStem.CONFIG.AXIAP1.Base DP:0x80004000

Meaning: The control register block of the AXI access ports starts at address 0x80004000.

**JTAGAPn.Base <address>**

This command informs the debugger about the start address of the register block of the “JTAGAPn:” access port. And this way it notifies the existence of the access port. An access port typically provides a control register block which needs to be accessed by the debugger to read/write from/to the bus connected to the access port.

**Example:** SYStem.CONFIG.JTAGAP1.Base DP:0x80005000

Meaning: The control register block of the JTAG access ports starts at address 0x80005000.

## <parameters> describing debug and trace “Components”

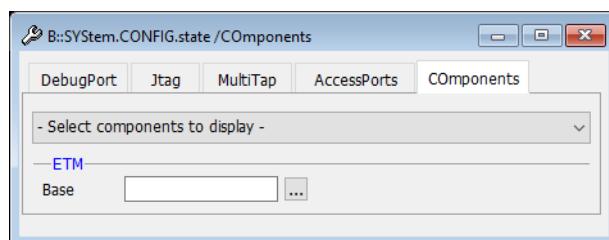

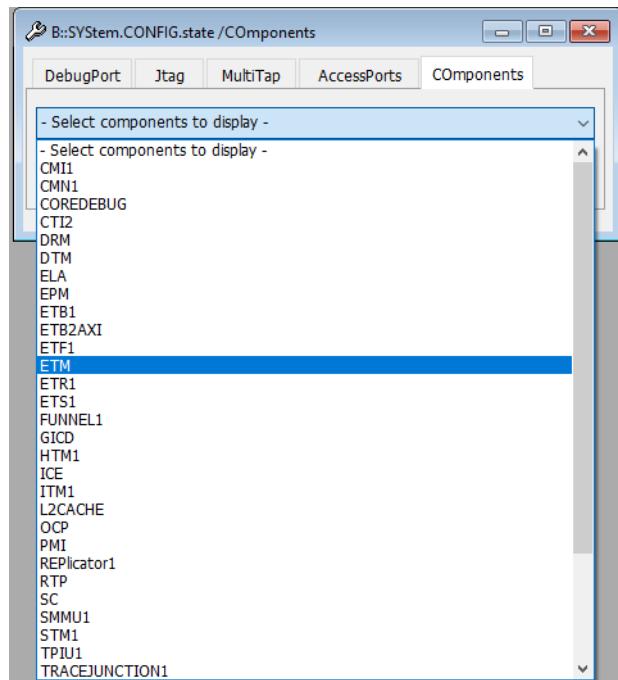

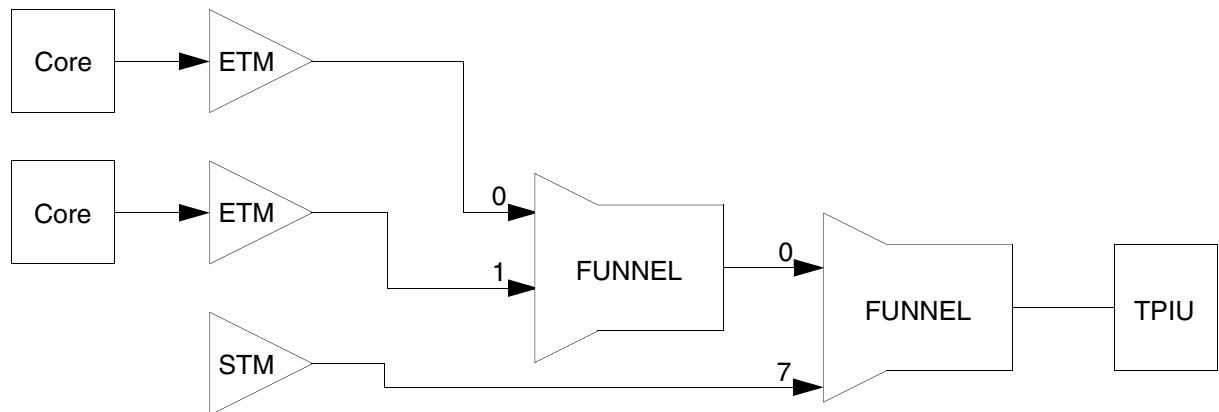

On the **Components** tab in the **SYStem.CONFIG.state** window, you can comfortably add the debug and trace components your chip includes and which you intend to use with the debugger's help.

Each configuration can be done by a command in a script file as well. Then you do not need to enter everything again on the next debug session. If you press the button with the three dots you get the corresponding command in the command line where you can view and maybe copy it into a script file.

You can have several of the following components: CMI, ETB, ETF, ETR, FUNNEL, STM.

**Example:** FUNNEL1, FUNNEL2, FUNNEL3,...

The <address> parameter can be just an address (e.g. 0x80001000) or you can add the access class in front (e.g. AHB:0x80001000). Without access class it gets the command specific default access class which is "EDAP." in most cases.

**Example:**

```

SYStem.CONFIG.COREDEBUG.Base 0x80010000 0x80012000

SYStem.CONFIG.ETM.Base 0x8001c000 0x8001d000

SYStem.CONFIG.STM1.Base EAHB:0x20008000

SYStem.CONFIG.STM1.Type ARM

SYStem.CONFIG.STM1.Mode STPv2

SYStem.CONFIG.FUNNEL1.Base 0x80004000

SYStem.CONFIG.FUNNEL2.Base 0x80005000

SYStem.CONFIG.TPIU.Base 0x80003000

SYStem.CONFIG.FUNNEL1.ATBSource ETM.0 0 ETM.1 1

SYStem.CONFIG.FUNNEL2.ATBSource FUNNEL1 0 STM1 7

SYStem.CONFIG.TPIU.ATBSource FUNNEL2

```

... .ATBSource <source>

Specify for components collecting trace information from where the trace data are coming from. This way you inform the debugger about the interconnection of different trace components on a common trace bus.

You need to specify the "... .Base <address>" or other attributes that define the amount of existing peripheral modules before you can describe the interconnection by "... .ATBSource <source>".

A CoreSight trace FUNNEL has eight input ports (port 0-7) to combine the data of various trace sources to a common trace stream. Therefore you can enter instead of a single source a list of sources and input port numbers.

#### Example:

SYStem.CONFIG FUNNEL.ATBSource ETM 0 HTM 1 STM 7

Meaning: The funnel gets trace data from ETM on port 0, from HTM on port 1 and from STM on port 7.

In an SMP (Symmetric MultiProcessing) debug session where you used a list of base addresses to specify one component per core you need to indicate which component in the list is meant:

**Example:** Four cores with ETM modules.

SYStem.CONFIG ETM.Base 0x1000 0x2000 0x3000 0x4000

SYStem.CONFIG FUNNEL1.ATBSource ETM.0 0 ETM.1 1

ETM.2 2 ETM.3 3

"...2" of "ETM.2" indicates it is the third ETM module which has the base address 0x3000. The indices of a list are 0, 1, 2, 3,... If the numbering is accelerating, starting from 0, without gaps, like the example above then you can shorten it to

SYStem.CONFIG FUNNEL1.ATBSource ETM

**Example:** Four cores, each having an ETM module and an ETB module.

SYStem.CONFIG ETM.Base 0x1000 0x2000 0x3000 0x4000

SYStem.CONFIG ETB.Base 0x5000 0x6000 0x7000 0x8000

SYStem.CONFIG ETB.ATBSource ETM.2 2

The third "ETM.2" module is connected to the third ETB. The last "2" in the command above is the index for the ETB. It is not a port number which exists only for FUNNELs.

For a list of possible components including a short description see [Components and Available Commands](#).

... .BASE <address>

This command informs the debugger about the start address of the register block of the component. And this way it notifies the existence of the component. An on-chip debug and trace component typically provides a control register block which needs to be accessed by the debugger to control this component.

**Example:** SYStem.CONFIG ETMBASE APB:0x8011c000

Meaning: The control register block of the Embedded Trace Macrocell (ETM) starts at address 0x8011c000 and is accessible via APB bus.

In an SMP (Symmetric MultiProcessing) debug session you can enter for the components COREBEBUG, CTI, ETB, ETF, ETM, ETR a list of base addresses to specify one component per core.

**Example assuming four cores:** SYStem.CONFIG

COREDEBUG.Base 0x80001000 0x80003000 0x80005000

0x80007000

For a list of possible components including a short description see [Components and Available Commands](#).

**... .Name** The name is a freely configurable identifier to describe how many instances exists in a target systems chip. TRACE32 PowerView GUI shares with other opened PowerView GUIs settings and the state of components identified by the same name and component type. Components using different names are not shared. Other attributes as the address or the type are used when no name is configured.

**Example 1: Shared None-Programmable Funnel:**

PowerView1:

SYStem.CONFIG.FUNNEL.PROGramable OFF

SYStem.CONFIG.FUNNEL.Name "shared-funnel-1"

PowerView2:

SYStem.CONFIG.FUNNEL.PROGramable OFF

SYStem.CONFIG.FUNNEL.Name "shared-funnel-1"

SYStem.CONFIG.Core 2. 1. ; merge configuration to describe a target system with one chip containing a single none-programmable FUNNEL.

**Example 2: Cluster ETFs:**

1. Configures the ETF base address and access for each core

SYStem.CONFIG.ETF.Base DAP:0x80001000 \

APB:0x80001000 DAP:0x80001000 APB:0x80001000

2. Tells the system the core 1 and 3 share cluster-ETF-1 and core 2 and 4 share cluster-ETF-2 despite using the same address for all ETFs

SYStem.CONFIG.ETF.Name "cluster-ETF-1" "cluster-ETF-2" \

"cluster-ETF-1" "cluster-ETF-2"

**... .NoFlush [ON | OFF]** Deactivates a component flush request at the end of the trace recording. This is a workaround for a bug on a certain chip. You will lose trace data at the end of the recording. Don't use it if not needed. Default: OFF.

**... .RESet** Undo the configuration for this component. This does not cause a physical reset for the component on the chip.

For a list of possible components including a short description see [Components and Available Commands](#).

**... .Size <size>** Specifies the size of the component. The component size can normally be read out by the debugger. Therefore this command is only needed if this can not be done for any reason.

... .SStackMode[NotAvailbale

| TRGETM | FULLTIDRM |

NOTSET | FULLSTOP |

FULLCTI]

Specifies the which method is used to implement the Stack mode of the on-chip trace.

**NotAvailable:** stack mode is not available for this on-chip trace.

**TRGETM:** the trigger delay counter of the onchip-trace is used. It starts by a trigger signal that must be provided by a trace source. Usually those events are routed through one or more CTIs to the on-chip trace.

**FULLTIDRM:** trigger mechanism for TI devices.

**NOTSET:** the method is derived by other GUIs or hardware detection.

**FULLSTOP:** on-chip trace stack mode by implementation.

**FULLCTI:** on-chip trace provides a trigger signal that is routed back to on-chip trace over a CTI.

... .view

Opens a window showing the current configuration of the component.

For a list of possible components including a short description see [Components and Available Commands](#).

... .TraceID <id>

Identifies from which component the trace packet is coming from. Components which produce trace information (trace sources) for a common trace stream have a selectable ".TraceID <id>".

If you miss this SYStem.CONFIG command for a certain trace source (e.g. ETM) then there is a dedicated command group for this component where you can select the ID (ETM.TraceID <id>).

The default setting is typically fine because the debugger uses different default trace IDs for different components.

For a list of possible components including a short description see [Components and Available Commands](#).

**CTI.Config <type>**

Informs about the interconnection of the core Cross Trigger Interfaces (CTI). Certain ways of interconnection are common and these are supported by the debugger e.g. to cause a synchronous halt of multiple cores.

NONE: The CTI is not used by the debugger.

ARMV1: This mode is used for ARM7/9/11 cores which support synchronous halt, only.

ARMPostInit: Like ARMV1 but the CTI connection differs from the ARM recommendation.

OMAP3: This mode is not yet used.

TMS570: Used for a certain CTI connection used on a TMS570 derivative.

CortexV1: The CTI will be configured for synchronous start and stop via CTI. It assumes the connection of DBGRQ, DBGACK, DBGRESTART signals to CTI are done as recommended by ARM. The CTIBASE must be notified. "CortexV1" is the default value if a Cortex-A/R core is selected and the CTIBASE is notified.

QV1: This mode is not yet used.

ARMV8V1: Channel 0 and 1 of the CTM are used to distribute start/stop events from and to the CTIs. ARMv8 only.

ARMV8V2: Channel 2 and 3 of the CTM are used to distribute start/stop events from and to the CTIs. ARMv8 only.

ARMV8V3: Channel 0, 1 and 2 of the CTM are used to distribute start/stop events. Implemented on request. ARMv8 only.

**ETR.CATUBase <address>**

Base address of the CoreSight Address Translation Unit (CATU).

**FUNNEL.Name <string>**

It is possible that different funnels have the same address for their control register block. This assumes they are on different buses and for different cores. In this case it is needed to give the funnel different names to differentiate them.

**FUNNEL.PROGrammable

[ON | OFF]**

Default is ON. If set to ON the peripheral is controlled by TRACE32 in order to route ATB trace data through the ATB bus network. If PROGrammable is configured to value OFF then TRACE32 will not access the FUNNEL registers and the base address doesn't need to be configured. This can be useful for FUNNELs that don't have registers or when those registers are read-only. TRACE32 need still be aware of the connected ATB trace sources and sink in order to know the ATB topology. To build a complete topology across multiple instances of PowerView the property Name should be set at all instances to a chip wide unique identifier.

**HTM.Type [CoreSight | WPT]**

Selects the type of the AMBA AHB Trace Macrocell (HTM). CoreSight is the type as described in the ARM CoreSight manuals. WPT is a NXP proprietary trace module.

|                                                             |                                                                                                                                                                                                                                                                                                      |

|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>STM.Mode</b> [NONE   XTIv2   SDTI   STP   STP64   STPv2] | Selects the protocol type used by the System Trace Module (STM).                                                                                                                                                                                                                                     |

| <b>STM.Type</b> [None   Generic   ARM   SDTI   TI]          | Selects the type of the System Trace Module (STM). Some types allow to work with different protocols (see STM.Mode).                                                                                                                                                                                 |

| <b>TPIU.Type</b> [CoreSight   Generic]                      | <p>Selects the type of the Trace Port Interface Unit (TPIU).</p> <p>CoreSight: Default. CoreSight TPIU. TPIU control register located at TPIU.Base &lt;address&gt; will be handled by the debugger.</p> <p>Generic: Proprietary TPIU. TPIU control register will not be handled by the debugger.</p> |

## Components and Available Commands

---

See the description of the commands above. Please note that there is a common description for ... .ATBSource, ... .Base, , ... .RESet, ... .TraceID.

**COREDEBUG.Base** <address>

**COREDEBUG.RESet**

Core Debug Register - ARM debug register, e.g. on Cortex-A/R

Some cores do not have a fix location for their debug register used to control the core. In this case it is essential to specify its location before you can connect by e.g. SYStem.Up.

**CTI.Base** <address>

**CTI.Config** [NONE | ARMV1 | ARMPostInit | OMAP3 | TMS570 | CortexV1 | QV1]

**CTI.RESet**

Cross Trigger Interface (CTI) - ARM CoreSight module

If notified the debugger uses it to synchronously halt (and sometimes also to start) multiple cores.

**ETB.ATBSource** <source>

**ETB.Base** <address>

**ETB.RESet**

**ETB.Size** <size>

Embedded Trace Buffer (ETB) - ARM CoreSight module

Enables trace to be stored in a dedicated SRAM. The trace data will be read out through the debug port after the capturing has finished.

**ETF.ATBSource** <source>

**ETF.Base** <address>

**ETF.RESet**

Embedded Trace FIFO (ETF) - ARM CoreSight module

On-chip trace buffer used to lower the trace bandwidth peaks.

**ETM.Base** <address>

**ETM.RESet**

Embedded Trace Macrocell (ETM) - ARM CoreSight module

Program Trace Macrocell (PTM) - ARM CoreSight module

Trace source providing information about program flow and data accesses of a core.

The ETM commands will be used even for PTM.

**ETR.ATBSource** <source>

**ETR.CATUBase** <address>

**ETR.Base** <address>

**ETR.RESet**

Embedded Trace Router (ETR) - ARM CoreSight module

Enables trace to be routed over an AXI bus to system memory or to any other AXI slave.

**FUNNEL.ATBSource** <sourcelist>

**FUNNEL.Base** <address>

**FUNNEL.Name** <string>

**FUNNEL.PROGrammable** [ON | OFF]

**FUNNEL.RESet**

CoreSight Trace Funnel (CSTF) - ARM CoreSight module

Combines multiple trace sources onto a single trace bus (ATB = AMBA Trace Bus).

**REP.ATBSource** <sourcelist>

**REP.Base** <address>

**REP.Name** <string>

**REP.RESet**

CoreSight Replicator - ARM CoreSight module

This command group is used to configure ARM Coresight Replicators with programming interface. After the Replicator(s) have been defined by the base address and optional names the ATB sources REPlicatorA and REPlicatorB can be used from other ATB sinks to connect to output A or B to the Replicator.

**HTM.Base** <address>

**HTM.RESet**

**HTM.Type** [CoreSight | WPT]

AMBA AHB Trace Macrocell (HTM) - ARM CoreSight module

Trace source delivering trace data of access to an AHB bus.

**STM.Base** <address>

**STM.Mode** [NONE | XTIv2 | SDTI | STP | STP64 | STPv2]

**STM.RESet**

**STM.Type** [None | Generic | ARM | SDTI | TI]

System Trace Macrocell (STM) - MIPI, ARM CoreSight, others

Trace source delivering system trace information e.g. sent by software in printf() style.

**TPIU.ATBSource** <source>

**TPIU.Base** <address>

**TPIU.RESet**

**TPIU.Type** [CoreSight | Generic]

Trace Port Interface Unit (TPIU) - ARM CoreSight module

Trace sink sending the trace off-chip on a parallel trace port (chip pins).

In the last years the chips and its debug and trace architecture became much more complex. Especially the CoreSight trace components and their interconnection on a common trace bus required a reform of our commands. The new commands can deal even with complex structures.

### ... **BASE** <address>

This command informs the debugger about the start address of the register block of the component. And this way it notifies the existence of the component. An on-chip debug and trace component typically provides a control register block which needs to be accessed by the debugger to control this component.

**Example:** SYStem.CONFIG ETMBASE APB:0x8011c000

Meaning: The control register block of the Embedded Trace Macrocell (ETM) starts at address 0x8011c000 and is accessible via APB bus.

In an SMP (Symmetric MultiProcessing) debug session you can enter for the components CORE, CTI, ETB, ETF, ETM, ETR a list of base addresses to specify one component per core.

Example assuming four cores: “SYStem.CONFIG COREBASE 0x80001000 0x80003000 0x80005000 0x80007000”.

For a list of possible components including a short description see [Components and Available Commands](#).

### ... **PORT** <port>

Informs the debugger about which trace source is connected to which input port of which funnel. A CoreSight trace funnel provides 8 input ports (port 0-7) to combine the data of various trace sources to a common trace stream.

**Example:** SYStem.CONFIG STMFUNNEL2PORT 3

Meaning: The System Trace Module (STM) is connected to input port #3 on FUNNEL2.

On an SMP debug session some of these commands can have a list of <port> parameter.

In case there are dedicated funnels for the ETB and the TPIU their base addresses are specified by ETBFUNNELBASE, TPIUFUNNELBASE respectively. And the funnel port number for the ETM are declared by ETMETBFUNNELPORT, ETMTPIUFUNNELPORT respectively.

For a list of possible components including a short description see [Components and Available Commands](#).

**CTICONFIG** <type>

Informs about the interconnection of the core Cross Trigger Interfaces (CTI). Certain ways of interconnection are common and these are supported by the debugger e.g. to cause a synchronous halt of multiple cores.

NONE: The CTI is not used by the debugger.

ARMV1: This mode is used for ARM7/9/11 cores which support synchronous halt, only.

ARMPostInit: Like ARMV1 but the CTI connection differs from the ARM recommendation.

OMAP3: This mode is not yet used.

TMS570: Used for a certain CTI connection used on a TMS570 derivative.

CortexV1: The CTI will be configured for synchronous start and stop via CTI. It assumes the connection of DBGRQ, DBGACK, DBGRESTART signals to CTI are done as recommended by ARM. The CTIBASE must be notified. "CortexV1" is the default value if a Cortex-A/R core is selected and the CTIBASE is notified.

QV1: This mode is not yet used.

**view**

Opens a window showing most of the SYStem.CONFIG settings and allows to modify them.

---

**Deprecated and New Commands**

In the following you find the list of deprecated commands which can still be used for compatibility reasons and the corresponding new command.

**SYStem.CONFIG** <parameter>

<parameter>:

(Deprecated)

<parameter>:

(New)

**COREBASE** <address>

**COREDEBUG.Base** <address>

**CTIBASE** <address>

**CTI.Base** <address>

**CTICONFIG** <type>

**CTI.Config** <type>

**DEBUGBASE** <address>

**COREDEBUG.Base** <address>

**ETBBASE** <address>

**ETB1.Base** <address>

**ETBFUNNELBASE** <address>

**FUNNEL4.Base** <address>

**ETFBASE** <address>

**ETF1.Base** <address>

**ETMBASE** <address>

**ETM.Base** <address>

**ETMETBFUNNELPORT** <port>

**FUNNEL4.ATBSource ETM** <port> (1)

**ETMFUNNEL2PORT** <port>

**FUNNEL2.ATBSource ETM** <port> (1)

|                                 |                                         |

|---------------------------------|-----------------------------------------|

| <b>ETMFUNNELPORT</b> <port>     | <b>FUNNEL1.ATBSource</b> ETM <port> (1) |

| <b>ETMTPIFUNNELPORT</b> <port>  | <b>FUNNEL3.ATBSource</b> ETM <port> (1) |

| <b>FUNNEL2BASE</b> <address>    | <b>FUNNEL2.Base</b> <address>           |

| <b>FUNNELBASE</b> <address>     | <b>FUNNEL1.Base</b> <address>           |

| <b>HSMBASE</b> <address>        | <b>HSM.Base</b> <address>               |

| <b>HTMBASE</b> <address>        | <b>HTM.Base</b> <address>               |

| <b>HTMETBFUNNELPORT</b> <port>  | <b>FUNNEL4.ATBSource</b> HTM <port> (1) |