# NAND FLASH Programming User's Guide

MANUAL

# NAND FLASH Programming User's Guide

---

**TRACE32 Online Help**

**TRACE32 Directory**

**TRACE32 Index**

|                                                                    |                                                                                     |

|--------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| <b>TRACE32 Documents</b> .....                                     |  |

| <b>FLASH Programming</b> .....                                     |  |

| <b>NAND FLASH Programming User's Guide</b> .....                   | <b>1</b>                                                                            |

| <b>    Introduction</b> .....                                      | <b>5</b>                                                                            |

| How This Manual is Organized                                       | 5                                                                                   |

| Related Documents                                                  | 6                                                                                   |

| Contacting Support                                                 | 6                                                                                   |

| <b>    List of Abbreviations</b> .....                             | <b>8</b>                                                                            |

| <b>    Background Information</b> .....                            | <b>8</b>                                                                            |

| What is a NAND Flash Device?                                       | 8                                                                                   |

| About Blocks, Pages, Main Area, and Spare Area                     | 9                                                                                   |

| About Bad Block Markers                                            | 10                                                                                  |

| About NAND Flash Controllers                                       | 11                                                                                  |

| <b>    Standard Approach</b> .....                                 | <b>12</b>                                                                           |

| Identifying and Running Scripts for NAND Flash Programming         | 12                                                                                  |

| If There Is No Script                                              | 14                                                                                  |

| <b>    Scripts for NAND Flash Programming</b> .....                | <b>15</b>                                                                           |

| Establishing Communication between Debugger and Target CPU         | 17                                                                                  |

| Configuring the NAND Flash Controller                              | 18                                                                                  |

| Resetting Default Values                                           | 20                                                                                  |

| Identifying the Type of NAND Flash Controller                      | 21                                                                                  |

| Informing TRACE32 about the NAND Flash Register Addresses          | 23                                                                                  |

| Informing TRACE32 about the NAND Flash Programming Algorithm       | 25                                                                                  |

| Identifying the Correct Driver Binary File for a NAND Flash Device | 27                                                                                  |

| File Name Convention for NAND Flash Drivers                        | 28                                                                                  |

| Finding the <nandflash_code> of a NAND Flash Device                | 29                                                                                  |

| Examples for Generic NFCs                                          | 31                                                                                  |

| Example for CPU-Specific NFCs                                      | 33                                                                                  |

| Checking the Identification from the NAND Flash Device             | 34                                                                                  |

| Erasing the NAND Flash Device                                      | 35                                                                                  |

| Programming the NAND Flash Device                                  | 36                                                                                  |

| Programming the Main Area                                          | 37                                                                                  |

| Verifying the Main Area                                            | 38                                                                                  |

|                                                                   |           |

|-------------------------------------------------------------------|-----------|

| Other Useful Commands (NAND)                                      | 39        |

| Writing Other File Formats to the Main Area                       | 39        |

| Modifying the Main Area                                           | 39        |

| Copying the Main Area                                             | 41        |

| Programming the Spare Area                                        | 43        |

| Programming the ECC Code to the Spare Area                        | 46        |

| Reading/Saving the NAND Flash Device                              | 47        |

| Reading the Main/Spare Area                                       | 47        |

| Full Examples: Generic NAND Flash Programming                     | 51        |

| Example 1                                                         | 51        |

| Example 2                                                         | 53        |

| Full Example: CPU-Specific NAND Flash Programming                 | 55        |

| <b>About OneNAND Flash Devices .....</b>                          | <b>56</b> |

| <b>Scripts for OneNAND Flash Devices .....</b>                    | <b>57</b> |

| Establishing Communication between Debugger and Target CPU        | 59        |

| Configuring the OneNAND Flash Bus                                 | 59        |

| Resetting Default Values                                          | 60        |

| Informing TRACE32 about the OneNAND Flash Address                 | 60        |

| Informing TRACE32 about the OneNAND Flash Programming Algorithm   | 61        |

| Identifying the Correct OneNAND Flash Driver for a OneNAND Device | 63        |

| Naming Convention for OneNAND Flash Drivers                       | 63        |

| Checking the Identification from the OneNAND Flash Device         | 65        |

| Erasing the OneNAND Flash Device                                  | 66        |

| Programming the OneNAND Flash Device                              | 67        |

| Programming the Main Area (OneNAND)                               | 67        |

| Verifying the Main Area (OneNAND)                                 | 68        |

| Other Useful Commands (OneNAND)                                   | 69        |

| Copying the Main Area (OneNAND)                                   | 69        |

| Modifying the Main Area (OneNAND)                                 | 71        |

| Programming the Spare Area (OneNAND)                              | 72        |

| Reading/Saving the OneNAND Flash Device                           | 75        |

| Reading the Main/Spare Area (OneNAND)                             | 75        |

| Saving the Main Area (OneNAND)                                    | 76        |

| Saving the Spare Area (OneNAND)                                   | 77        |

| Full Example                                                      | 79        |

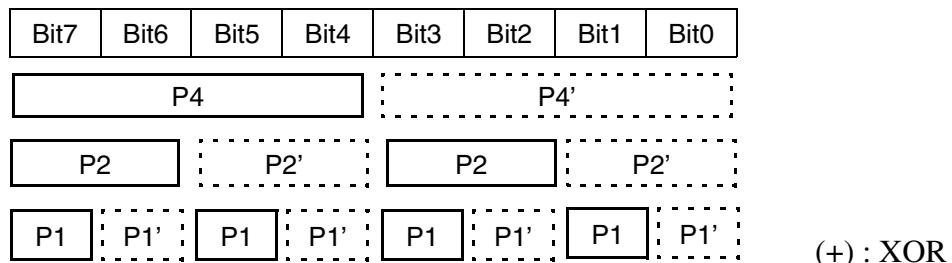

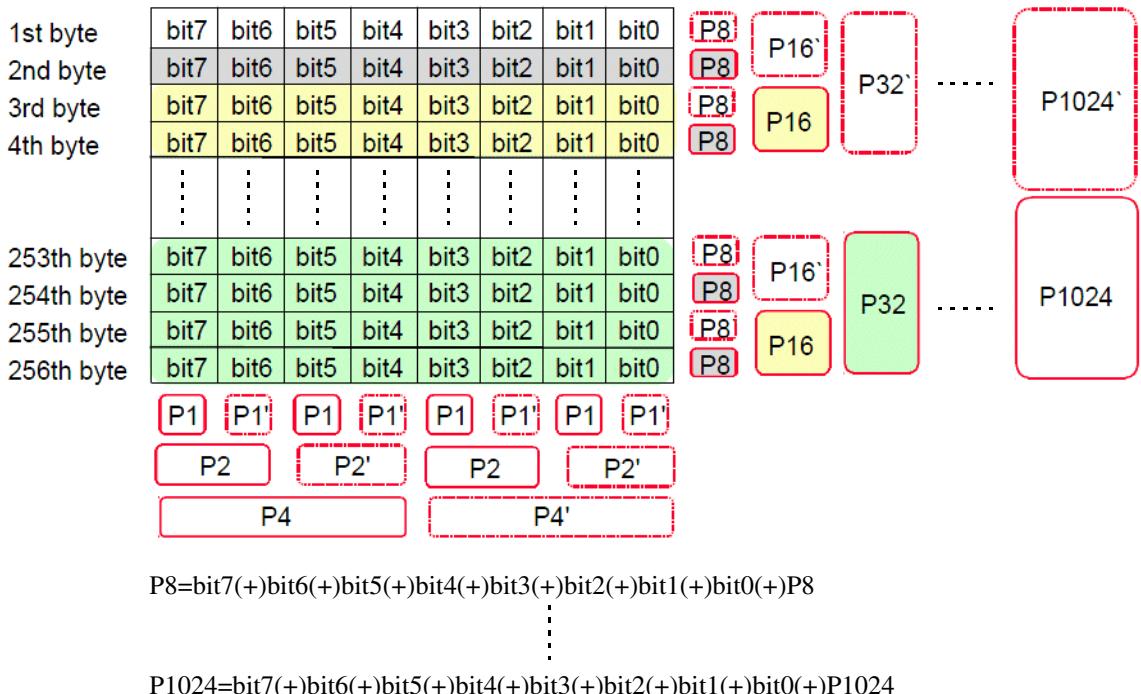

| <b>Appendix A: ECC (Error Correction Code) .....</b>              | <b>80</b> |

| How to Generate ECC and to Detect Error                           | 80        |

| 3bytes per 256bytes ECC codes                                     | 82        |

| 3bytes per 512bytes ECC Codes                                     | 83        |

| <b>Appendix B: Spare Area Schemes .....</b>                       | <b>84</b> |

| Linux MTD NAND Driver Default Spare Area Schemes                  | 84        |

| SAMSUNG Standard Spare Area Schemes                               | 86        |

## Introduction

---

This manual describes the basic concept of NAND and OneNAND Flash programming.

There are many similarities between NAND Flash programming and OneNAND Flash programming, but also important differences. For reasons of clarity and user-friendliness, this manual covers NAND Flash programming and OneNAND Flash programming in separate chapters.

## How This Manual is Organized

---

- **Background Information:** Provides information about important terms in NAND Flash programming, including the different types of NAND Flash controllers (NFC).

- **Standard Approach:** Describes the fastest way to get started with NAND Flash programming. All you need to do is to identify and run the correct script.

Demo scripts for NAND Flash programming are available in the folder:

`~/demo/<architecture>/flash/<cpu_name>-<nand_flash_code>.cmm`

e.g. `omap3430-nand.cmm`, `imx31-nand2g08.cmm` ...

- **Scripts for NAND Flash Programming:** Describes how you can create a script if there is no demo script for the NFC type you are using.

- **About OneNAND Flash Devices:** Explains the difference between OneNAND Flash and NAND Flash.

- **Scripts for OneNAND Flash Devices:** Describes how you can create scripts for OneNAND Flash programming based on the template script provided by Lauterbach.

- **Appendix A and B:** Provide information about ECC (error correction code) and spare area schemes.

## Related Documents

---

A complete description of all NAND Flash programming commands can be found in chapter “**FLASHFILE**” in “**General Commands Reference Guide F**” (general\_ref\_f.pdf).

The manual “**List of Supported FLASH Devices**” (flashlist.pdf) provides the following information:

- A list of the supported NAND and OneNAND Flash devices.

- A list of the supported on-chip NAND Flash controllers.

The Lauterbach home page provides an up-to-date list of

- Supported NAND and OneNAND Flash devices under:

<https://www.lauterbach.com/ylist.html>

- Supported on-chip NAND Flash controllers under:

<https://www.lauterbach.com/ylistnand.html>

## Contacting Support

---

Use the Lauterbach Support Center: <https://support.lauterbach.com>

- To contact your local TRACE32 support team directly.

- To register and submit a support ticket to the TRACE32 global center.

- To log in and manage your support tickets.

- To benefit from the TRACE32 knowledgebase (FAQs, technical articles, tutorial videos) and our tips & tricks around debugging.

Or send an email in the traditional way to [support@lauterbach.com](mailto:support@lauterbach.com).

Be sure to include detailed system information about your TRACE32 configuration.

1. To generate a system information report, choose **TRACE32 > Help > Support > Systeminfo**.

Generate TRACE32 Support Information

Press the following button to get help on how to generate Support Information:

|             |                              |                                     |                      |

|-------------|------------------------------|-------------------------------------|----------------------|

| Company:    | Lauterbach                   | Department:                         | <input type="text"/> |

| Prefix:     | <input type="text"/>         | P.O. Box:                           | <input type="text"/> |

| Firstname:  | Andrea                       | ZIP Code:                           | 85635                |

| Surname:    | Martin                       |                                     |                      |

| Street:     | Altlauferstr. 40             |                                     |                      |

| City:       | Hoehenkirchen-Siegrtsbr.     |                                     |                      |

| Country:    | Germany                      |                                     |                      |

| Telephone:  | (+49) 8102-9876-555          |                                     |                      |

| eMail:      | andrea.martin@lauterbach.com |                                     |                      |

| Product:    | PowerTrace PX                |                                     |                      |

| Target CPU: | ARM940T                      |                                     |                      |

| Hostsystem: | Windows 10                   |                                     |                      |

| Compiler:   | Arm                          |                                     |                      |

| RealtimeOS: | None                         | Safe Mode: <input type="checkbox"/> |                      |

Generate Support Information:

**NOTE:** Please help to speed up processing of your support request. By filling out the system information form completely and with correct data, you minimize the number of additional questions and clarification request e-mails we need to resolve your problem.

2. Preferred: click **Save to File**, and send the system information as an attachment to your e-mail.

3. Click **Save to Clipboard**, and then paste the system information into your e-mail.

**NOTE:** In case of missing script files (\*.cmm), please proceed as requested in "[If There is No Script](#)".

|            |                       |

|------------|-----------------------|

| <b>ALE</b> | Address latch enable  |

| <b>CLE</b> | Command latch enable  |

| <b>CS</b>  | Chip selection        |

| <b>ECC</b> | Error correction code |

| <b>NFC</b> | NAND Flash controller |

| <b>SP</b>  | Spare area            |

## Background Information

---

This chapter of the manual is aimed at users who are new to NAND Flash programming; it does not address experts with many years of expertise in this area. This chapter gives you a brief overview of important terms in NAND Flash programming, such as NAND Flash device, block, page, main area, spare area, bad block marker, generic NFC, CPU-specific NFC.

## What is a NAND Flash Device?

---

A NAND Flash device (short: NAND Flash) is a non-volatile storage chip that can be electrically erased and reprogrammed. It is used in data-storage applications such as cell phones and multi-media devices. Reasons why NAND Flash devices have become widespread include:

- Smaller interface pins than NOR Flash

- High density at low-cost per bit

- Faster than NOR Flash

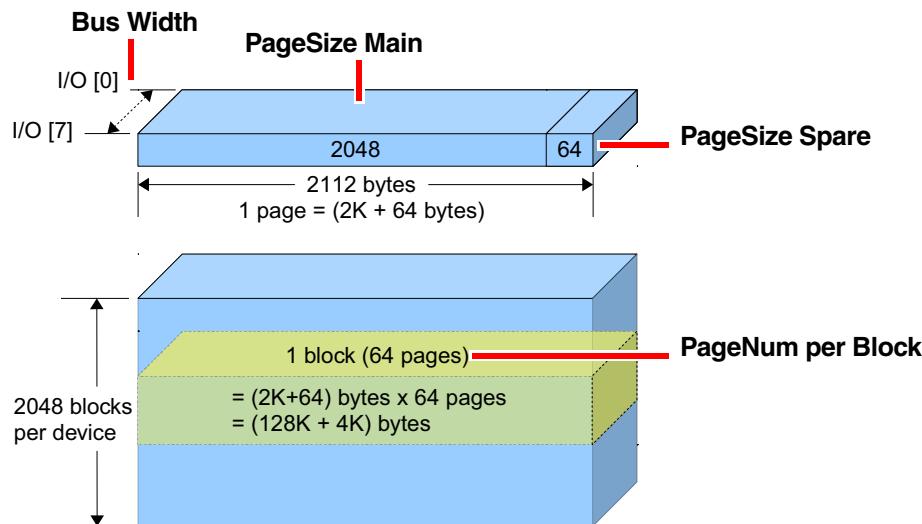

# About Blocks, Pages, Main Area, and Spare Area

---

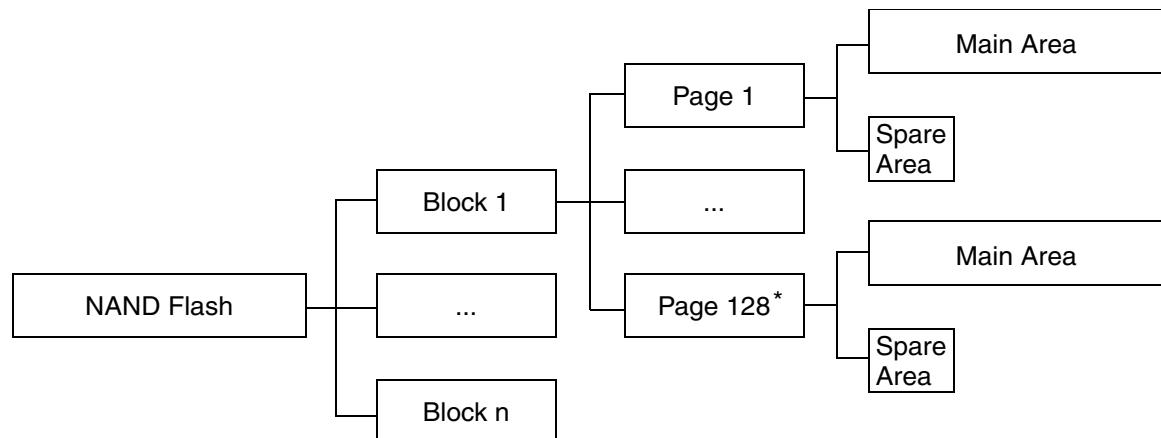

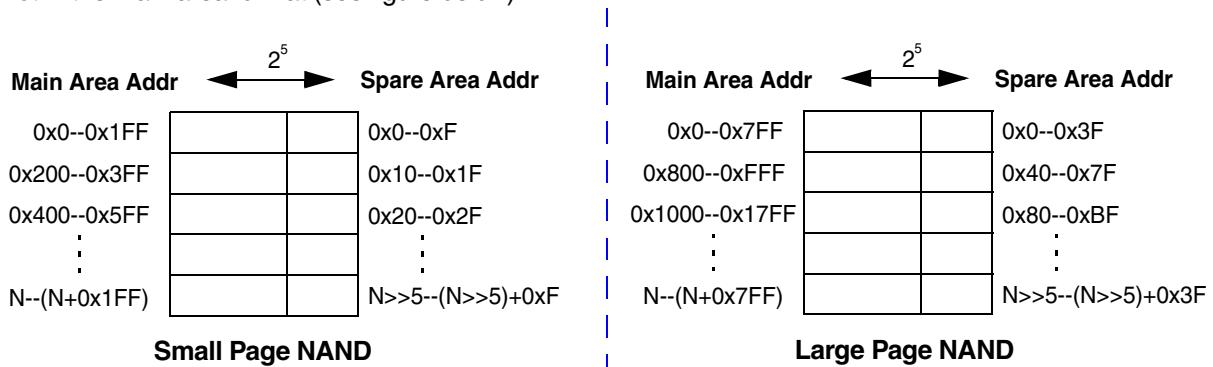

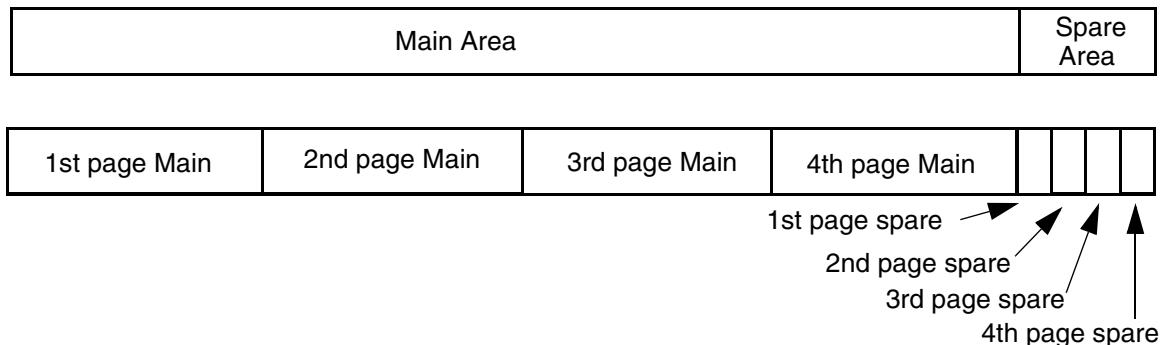

A NAND Flash consists of blocks. Each block is subdivided into 32, 64, or 128 pages, and each page has a main and a spare area; see example diagram below.

\*) 32, 64 or 128 pages

**Block** A block is the minimum size unit for erasing.

**Page** A page is the minimum size unit for reading and writing.

There are two types of pages:

- Small pages

- Large pages

| Type              | Main Area*  | Spare Area* | Total* |

|-------------------|-------------|-------------|--------|

| <b>Small Page</b> | 256         | 8           | 264    |

|                   | 512         | 16          | 528    |

| <b>Large Page</b> | 2048        | 64          | 2112   |

|                   | 4096        | 128         | 4224   |

|                   | *) in Bytes |             |        |

**Main area** The main area of each page can have a size of 512, 2048, or 4096 Bytes and contains the real code or data.

**Spare area** The spare area of each page can have a size of 16, 32, 64, or 128 Bytes and contains the following:

- Bad block marker for a bad block (mandatory)

- ECC codes (optional)

- User-specific metadata (optional)

## About Bad Block Markers

If a block is bad, then data cannot be erased or read from or written to the bad block. To flag a bad block, one or two bad block markers are used:

- The 1st marker is located in the spare area of the 1st page.

- The 2nd marker is located in the spare area of the 2nd page.

Bad block markers are stored in different byte positions, depending on the type of page (large or small):

- **Large page NAND:** The bad block marker is stored in the 1st byte.

- **Small page NAND:** The bad block marker is stored in the 6th byte.

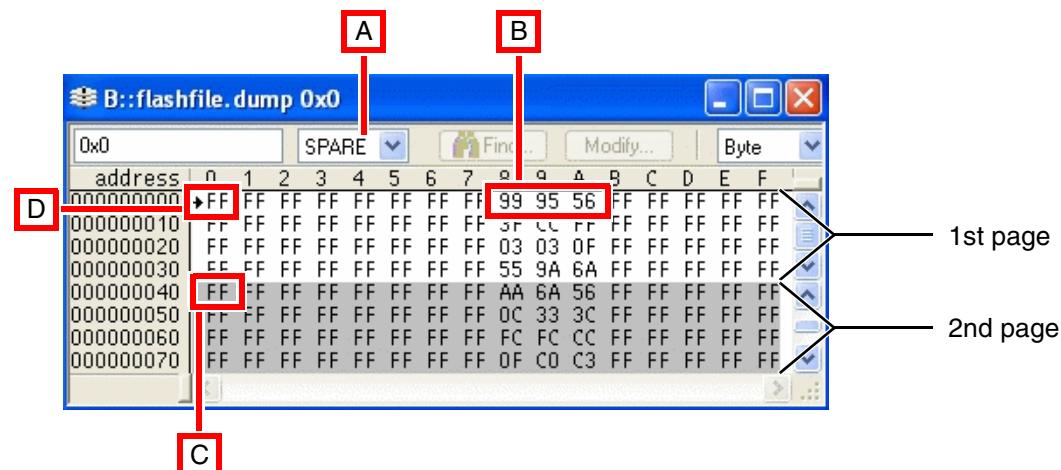

The figure below shows the 64-byte spare areas of the first two pages of a large page NAND. The **FLASHFILE.DUMP** window visualizes the individual pages using alternating colors for pages - white and gray.

- A** Spare area of a large page NAND

- B** ECC code

- C, D**

- FF = The block that these first two pages (white and gray) belong to is intact.

- If **[C]** or **[D]** or both do *not* read FF, as shown above, then the system considers the block to be bad.

Byte position of a 1st bad block marker in the 1st page = [D].

Byte position of a 2nd bad block marker in the 1st page = [B].

**NOTE:** The **/EraseBadBlocks** option of the **FLASHFILE.Erase** command can only erase faked bad blocks, but not real bad blocks. A faked bad block is a block where the user has modified an FF value to a non-FF value in the byte position **[C]** or **[D]** or in both byte positions.

# About NAND Flash Controllers

---

Access to the NAND Flash is performed by an on-chip NAND Flash controller. There are two types of NAND Flash controllers (NFC):

- **Generic NAND Flash controllers**

These NFC types are typically manufactured by Samsung Semiconductor, Atmel Corporation, STMicroelectronics, Marvell, Inc., and Texas Instruments.

- **CPU-specific NAND Flash controllers**

These NFC types are typically manufactured by Qualcomm, Freescale Semiconductor, NVIDIA Corporation, and Renesas Technology, Corp.

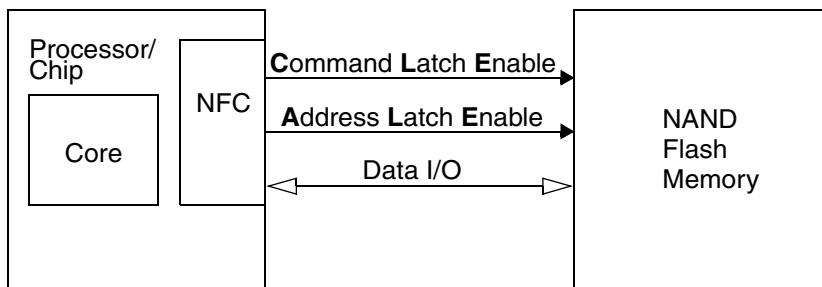

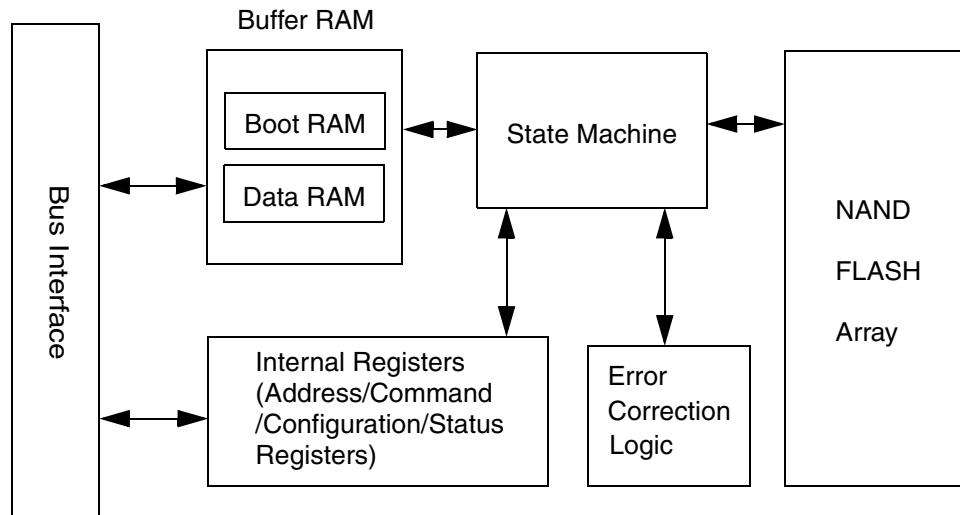

The architecture of systems featuring generic NFCs is shown in the block diagram below.

**Figure:** System with a Generic NAND Flash Controller (NFC)

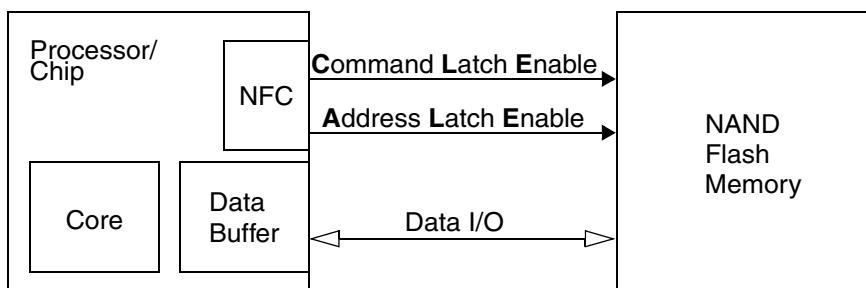

The architectures of systems featuring CPU-specific NFCs may vary considerably. The following block diagram illustrates an example of a typical architecture. Data from/to the NAND Flash is buffered in a data buffer.

**Figure:** Example of a System with a CPU-specific NAND Flash Controller (NFC)

# Standard Approach

---

The chapter “Standard Approach” provides a compact description of the steps required to program NAND Flash memory. This description is intentionally restricted to standard use cases.

## Overview of the Standard Approach:

- [Identify and run the required script for NAND Flash programming](#) based on information on our website.

- [What to do if there is no script for NAND Flash programming](#).

The following step-by-step procedures describe the standard approach in detail.

A detailed description of the NAND Flash programming concepts is given in “[Scripts for NAND Flash Programming](#)”.

## Identifying and Running Scripts for NAND Flash Programming

---

Demo scripts (\*.cmm) for NAND Flash programming are provided by Lauterbach. They can be found in the TRACE32 installation directory, which contains scripts developed for generic and CPU-specific NFC types.

### Path and file name convention of scripts for generic and CPU-specific NFC types:

`~/demo/<architecture>/flash/<cpu_name>-<prefix_of_nand_flash_code>.cmm`

### To identify and run the required script:

1. Make a note of the `<cpu_name>` printed on the CPU; for example, at91sam9xe

2. For information about supported Flash devices, access the [Lauterbach](#) website.

3. Click the + tree button next to **Tool Chain**, and then click **Supported Flash Devices** (<https://www.lauterbach.com/ylist.html>).

4. On the **Supported Flash Devices** page, select the required company from the drop-down list.

**Supported FLASH Devices**

LAUTERBACH

content

- Supported Flash Devices

home > Tool Chain

Supported FLASH Devices

NAND FLASH devices are marked in GREEN.

SERIAL FLASH devices are marked in RED.

5. Use the type printed on the Flash device to retrieve the <nand\_flash\_code> from the web page.

For example, NAND Flash type = MT29F2G08

| TYPE        | COMPANY | CODE     | COMMENT     |

|-------------|---------|----------|-------------|

| 28F00AM29EW | MICRON  | M29EW    | 16-bit mode |

|             |         | M29EWB   | 8-bit mode  |

| ⋮           | ⋮       | ⋮        | ⋮           |

| MT29F1G16   | MICRON  | NAND1G16 | NAND Flash  |

| MT29F2G08   | MICRON  | NAND2G08 | NAND Flash  |

| MT29F2G16   | MICRON  | NAND2G16 | NAND Flash  |

| MT29F4G08   | MICRON  | NAND2G08 | NAND Flash  |

Result: <prefix\_of\_nand\_flash\_code> nand2g08 = nand

6. Put the <cpu\_name> and the prefix together to form the script name:

at91sam9xe-nand2g08.cmm

The script file resides in this folder: ~/demo/arm/flash/at91sam9xe-nand2g08.cmm

Where ~/ is expanded to the TRACE32 installation directory, which is c:/t32 by default.

If the folder does not contain the script you are looking for, see “[If There Is No Script](#)” on [page 14](#).

7. Run the script in TRACE32 by doing one of the following:

- Choose **File > Run Script <cmm\_script\_name>**

- In the command line, type **DO <cmm\_script\_name>**

**NOTE:**

Each script (\*.cmm) includes a reference to the required NAND Flash programming algorithm (\*.bin).

You do not need to program or select the algorithm.

**Example**

```

;

<code_range>      <data_range>      <algorithm_file>

FLASHFILE.TARGET 0x80008000++0x3fff 0x8000C000++0x4FFF

~~/demo/arm/flash/byte/nand2g08_imx.bin

```

# If There Is No Script

---

If there is no script for your device in this directory (~~/demo/<architecture>/flash/), then please send a request to **support@lauterbach.com** using the e-mail template below.

## E-Mail Template:

Chip name: \_\_\_\_\_

Name of NAND Flash device: \_\_\_\_\_

Provide the CPU datasheet for us: \_\_\_\_\_

Lend the target board to us by sending it to the address given in “[Contacting Support](#)”: \_\_\_\_\_

*<system\_information>*

Be sure to include detailed system information about your TRACE32 configuration. For information about how to create a system information report, see “[Contacting Support](#)”.

Normally we can provide support for a new device in two weeks.

If our support cannot provide you with a PRACTICE script, you will have to create your own PRACTICE script (\*.cmm).

For more information, see “[Scripts for NAND Flash Programming](#)” on [page 14](#).

# Scripts for NAND Flash Programming

---

This chapter describes how you can create your own scripts for chips that are equipped with generic or CPU-specific NAND Flash controllers.

The steps and the framework (see below) provide an overview of the process. Both, steps and framework, are described in detail in the following sections.

**The following steps are necessary to create a new script:**

1. [“Establishing Communication between Debugger and Target CPU”](#), page 17

2. [“Configuring the NAND Flash Controller”](#), page 18

3. [“Resetting Default Values”](#), page 20

4. [“Identifying the Type of NAND Flash Controller”](#), page 21

5. [“Informing TRACE32 about the NAND Flash Register Addresses”](#), page 23

6. [“Informing TRACE32 about the NAND Flash Programming Algorithm”](#), page 25

7. [“Checking the Identification from the NAND Flash Device”](#), page 34

8. [“Erasing the NAND Flash Device”](#), page 35

9. [“Programming the NAND Flash Device”](#), page 36

The following framework can be used as base for NAND Flash programming:

```

; Establish the communication

; between the target CPU and the

; TRACE32 debugger.

; Configure the NAND Flash

; controller.

FLASHFILE.RESET                                ; Reset the NAND Flash environment

; in TRACE32 to its default values.

FLASHFILE.CONFIG ...                            ; Inform TRACE32 about the

; NAND Flash register addresses.

FLASHFILE.TARGET ...                            ; Specify the NAND Flash

; programming algorithm and where

; it runs in the target RAM.

FLASHFILE.GETID                                ; Get the ID values of the NAND

; Flash device.

FLASHFILE.Erase ...                            ; Erase the NAND Flash.

FLASHFILE.LOAD <main_file> ...          ; Program the file to the NAND

; Flash (main area).

```

An ellipsis (...) in the framework indicates that command parameters have been omitted here for space economy.

|              |                                                                                                       |

|--------------|-------------------------------------------------------------------------------------------------------|

| <b>NOTE:</b> | The parametrization of <b>FLASHFILE.CONFIG</b> and <b>FLASHFILE.TARGET</b> requires expert knowledge. |

|--------------|-------------------------------------------------------------------------------------------------------|

# Establishing Communication between Debugger and Target CPU

---

NAND Flash programming with TRACE32 requires that the communication between the debugger and the target CPU is established. The following commands are available to set up this communication:

**SYStem.CPU** <cpu>

Specify your target CPU.

**SYStem.Up**

Establish the communication between the debugger and the target CPU.

```

SYStem.CPU OMAP3430      ; Select OMAP3430 as the target CPU.

```

```

SYStem.Up                ; Establish the communication between the

; debugger and the target CPU.

```

# Configuring the NAND Flash Controller

Programming a NAND Flash device requires a proper initialization of the NAND Flash controller. The following settings might be necessary:

- Enable the NAND Flash controller or bus.

- Configure the communication signals (clock, timing, etc.).

- Inform the NAND Flash controller about the NAND Flash device (large/small page, ECC, spare, etc.).

- Configure the NAND Flash pins if they are muxed with other functions of the CPU.

- Disable the write protection for the NAND Flash.

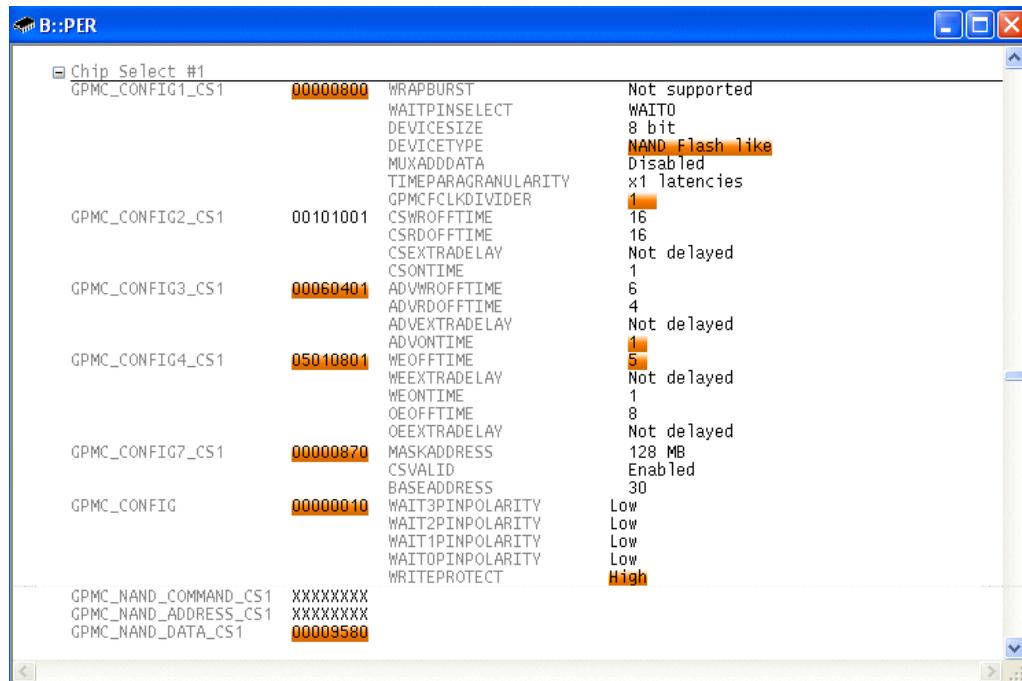

Use the **PER.view** command to check the settings for the NAND Flash controller.

The screenshot shows a software interface titled 'B:PER' with a window titled 'Chip\_Select #1'. The window displays a table of configuration parameters for a NAND Flash controller. The table has two columns: 'Parameter' and 'Value'. The parameters are grouped by section, indicated by bold text in the first column. The 'Value' column contains various settings, some of which are highlighted in orange. The sections and their values are as follows:

| Parameter             | Value           |

|-----------------------|-----------------|

| GPMC_CONFIG1_CS1      | 00000800        |

| WRAPBURST             | Not supported   |

| WAITPINSELECT         | WAIT0           |

| DEVICESIZE            | 8 bit           |

| DEVICETYPE            | NAND Flash like |

| MUXADDATA             | Disabled        |

| TIMEPARAGRANULARITY   | x1 latencies    |

| GPMCFCLKDIVIDER       | 1               |

| CSWRDFTIME            | 16              |

| CSRDOFTIME            | 16              |

| CSEXTRADELAY          | Not delayed     |

| CSONTIME              | 1               |

| ADVWRDFTIME           | 6               |

| ADVRDFTIME            | 4               |

| ADVEXTRADELAY         | Not delayed     |

| ADVONTIME             | 1               |

| WEOFFTIME             | 5               |

| WEEXTRADELAY          | Not delayed     |

| WEONTIME              | 1               |

| OEONTIME              | 8               |

| OEEXTRADELAY          | Not delayed     |

| GPMC_CONFIG7_CS1      | 00000870        |

| MASKADDRESS           | 128 MB          |

| CSVALID               | Enabled         |

| BASEADDRESS           | 30              |

| GPMC_CONFIG           | 00000010        |

| WAIT3PINPOLARITY      | Low             |

| WAIT2PINPOLARITY      | Low             |

| WAIT1PINPOLARITY      | Low             |

| WAIT0PINPOLARITY      | Low             |

| WRITERETECT           | High            |

| GPMC_NAND_COMMAND_CS1 | XXXXXXXX        |

| GPMC_NAND_ADDRESS_CS1 | XXXXXXXX        |

| GPMC_NAND_DATA_CS1    | 00009580        |

**Example: NAND Flash controller configuration for the OMAP3430.**

```

PER.Set SD:0x6E0000A8 %LE %Long 0x870 ; Enable CS1 and define

; the base address of

; CS1(NAND Flash).

; LE = little endian

PER.Set SD:0x6E000098 %LE %Long 0x60401 ; Define the NAND Flash

PER.Set SD:0x6E00009C %LE %Long 0x5010801 ; access timing.

PER.Set SD:0x6E000090 %LE %Long 0x0800 ; Define CS1 for 8 bit

; NAND Flash.

PER.Set SD:0x6E000050 %LE %Long 0x10 ; Disable the write

; protection of the NAND

; Flash device.

```

# Resetting Default Values

---

The following command is used to reset the NAND Flash environment in TRACE32 to its default values.

## **FLASHFILE.RESet**

Reset the NAND Flash environment

in TRACE32 to its default values.

# Identifying the Type of NAND Flash Controller

You need to know which NFC type you are dealing with because NAND Flash programming differs depending on the NFC type:

- Generic NAND Flash controllers

- CPU-specific NAND Flash controllers

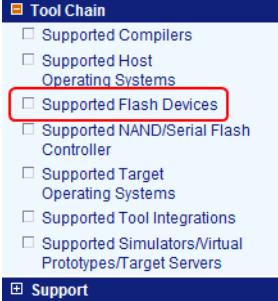

## To identify the type of controller:

1. Access the [Lauterbach](#) website.

2. Click the + tree button next to **Tool Chain**, and then click **Supported NAND/Serial Flash Controller**.

3. Select the required company from the drop-down list.

Supported NAND/SERIAL FLASH Controllers

LAUTERBACH

Supported NAND / Serial FLASH Controllers

Serial FLASH Controller are marked in RED.

MMC FLASH Controller are marked in BLUE.

4. Locate the desired CPU.

The **Controller** column indicates whether the NFC type is generic or CPU-specific or a hybrid. The following three examples cover all possible options.

### Example 1: CPU = OMAP3530

The entry in the **Controller** column reads *generic*, and the entry in the **Comment** column reads *NAND*. That means that this CPU is equipped with a generic NAND Flash controller.

| Tool Chain                                             | CONTROLLER  | COMMENT  |

|--------------------------------------------------------|-------------|----------|

| Supported Compilers                                    | STM32F103ZE | NAND     |

| Supported Host Operating Systems                       | STM32F10X   | SPI      |

| Supported Flash Devices                                | STR910      | SPI      |

| Supported NAND/Serial Flash Controller                 |             |          |

| Supported Target Operating Systems                     |             |          |

| Supported Tool Integrations                            |             |          |

| Supported Simulators/Virtual Prototypes/Target Servers |             |          |

| Support                                                | CONTROLLER  | COMMENT  |

| Support                                                | DM320       | NAND     |

| Sales                                                  | DM355       | NAND     |

| News / Events                                          | DM365       | NAND     |

| Company                                                | DM365       | SPI      |

| Chip Selection                                         | DM365       | eMMC     |

|                                                        | DM6443      | NAND     |

|                                                        | OMAP24XX    | NAND     |

|                                                        | OMAP34XX    | NAND     |

|                                                        | OMAP3530    | omap3530 |

|                                                        | OMAP35XX    | generic  |

|                                                        | OMAP4430    | omap4430 |

|                                                        | OMAPL138    | generic  |

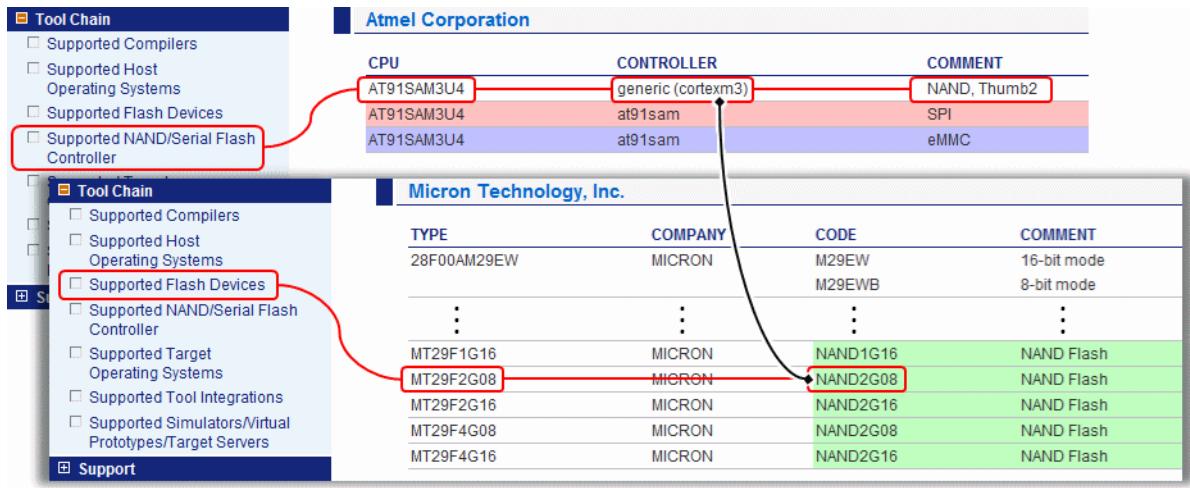

## Example 2: CPU = AT91SAM3U4

The entry in the **Controller** column reads *generic (cortexm3)*, and the entry in the **Comment** column reads *NAND, Thumb2*.

That means that this CPU is equipped with a generic NAND Flash controller, too. The term in parentheses tells you the architecture of the processor core, here *(cortexm3)*. This processor core requires that the NAND Flash driver binary file is compiled using a special instruction set, here *Thumb2*.

| Tool Chain                                                                      |

|---------------------------------------------------------------------------------|

| <input type="checkbox"/> Supported Compilers                                    |

| <input type="checkbox"/> Supported Host Operating Systems                       |

| <input type="checkbox"/> Supported Flash Devices                                |

| <input checked="" type="checkbox"/> Supported NAND/Serial Flash Controller      |

| <input type="checkbox"/> Supported Target Operating Systems                     |

| <input type="checkbox"/> Supported Tool Integrations                            |

| <input type="checkbox"/> Supported Simulators/Virtual Prototypes/Target Servers |

| <input type="checkbox"/> Support                                                |

| Atmel Corporation |                    |           |

|-------------------|--------------------|-----------|

| CPU               | CONTROLLER         | COMMENT   |

| AT91SAM3U4        | generic (cortexm3) | NAND, Thu |

| AT91SAM3U4        | at91sam            | SPI       |

| AT91SAM3U4        | at91sam            | eMMC      |

| ⋮                 | ⋮                  | ⋮         |

## Example 3: CPU = I.MX31

The entry in the **Controller** column contains the controller name *(imx)*, and the entry in the **Comment** column reads *NAND*. That means that this CPU is equipped with a CPU-specific NAND Flash controller.

| Tool Chain                                                                      |

|---------------------------------------------------------------------------------|

| <input type="checkbox"/> Supported Compilers                                    |

| <input type="checkbox"/> Supported Host Operating Systems                       |

| <input type="checkbox"/> Supported Flash Devices                                |

| <input checked="" type="checkbox"/> Supported NAND/Serial Flash Controller      |

| <input type="checkbox"/> Supported Target Operating Systems                     |

| <input type="checkbox"/> Supported Tool Integrations                            |

| <input type="checkbox"/> Supported Simulators/Virtual Prototypes/Target Servers |

| <input type="checkbox"/> Support                                                |

| <input type="checkbox"/> Sales                                                  |

| <input type="checkbox"/> News / Events                                          |

| <input type="checkbox"/> Company                                                |

| <input type="checkbox"/> Chip Selection                                         |

| Freescale Semiconductor, Inc. |            |           |

|-------------------------------|------------|-----------|

| CPU                           | CONTROLLER | COMMENT   |

| I.MX21                        | imx        | NAND      |

| I.MX23                        | gpmimx23   | NAND      |

| I.MX25                        | imx25      | NAND      |

| I.MX25                        | imx35      | SPI(CSPI) |

| I.MX27                        | imx        | NAND      |

| I.MX27                        | imx        | SPI(CSPI) |

| I.MX28                        | gpmimx28   | NAND      |

| I.MX31                        | imx        | NAND      |

| I.MX31                        | imx        | SPI(CSPI) |

| I.MX35                        | imx25      | NAND      |

| I.MX35                        | imx35      | SPI(CSPI) |

| MPC5121                       | mpc51xx    | NAND      |

# Informing TRACE32 about the NAND Flash Register Addresses

The parametrization of **FLASHFILE.CONFIG** differs for generic and CPU-specific NFCs.

## In the case of generic NAND Flash controllers:

The NAND Flash device can be programmed by operating the command, address, and I/O registers. As a result:

1. A generic NAND Flash programming driver can be used.

2. The command **FLASHFILE.CONFIG** always requires the parameters

`<cmd_reg> <addr_reg> <io_reg>`

**FLASHFILE.CONFIG** `<cmd_reg> <addr_reg> <io_reg>`

Inform TRACE32 about the NAND Flash register addresses.

| Parameters for <b>FLASHFILE.CONFIG</b> command – generic NAND Flash programming |                                           |

|---------------------------------------------------------------------------------|-------------------------------------------|

| <code>&lt;cmd_reg&gt;</code>                                                    | Register address of the command register  |

| <code>&lt;addr_reg&gt;</code>                                                   | Register address of the address register  |

| <code>&lt;io_reg&gt;</code>                                                     | Register address of the data I/O register |

For information about the register addresses of the command, address, and data I/O register, refer to the manufacturer's processor manual.

### Example 1:

```

; Register addresses of the generic NAND Flash controller in the OMAP3530

FLASHFILE.CONFIG 0x6E00007C 0x6E000080 0x6E000084

```

### Example 2:

```

; Register addresses of the generic NAND Flash controller in the OMAP3430

FLASHFILE.CONFIG 0x6E0000AC 0x6E0000B0 0x6E0000B4

```

## In the case of CPU-specific NAND Flash controllers:

**FLASHFILE.CONFIG** `<nfc_base_address> , ,`

Specify the start address of the NAND Flash base register.

, represents don't-care parameters.

For information about the NAND Flash base register, refer to the manufacturer's processor manual.

**Example:**

```

; NFC base address of the CPU-specific NAND Flash controller

; in the i.MX31.

FLASHFILE.CONFIG 0xB8000000 , ,

```

# Informing TRACE32 about the NAND Flash Programming Algorithm

The following command is available to inform TRACE32 about the NAND Flash programming algorithm (\*.bin):

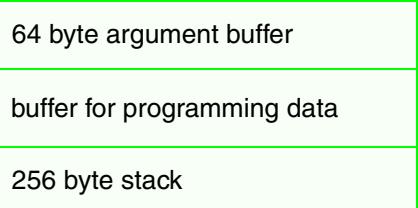

**FLASHFILE.TARGET** <code\_range> <data\_range> <file>

Specify the NAND Flash programming algorithm and where it runs in the target RAM.

## Parameters

- <code\_range>

Define an address range in the target's RAM to which the NAND Flash programming algorithm is loaded.

Flash algorithm

32 byte

**Figure:** Memory mapping for the <code\_range>

Required size for the code is: size\_of(<file>) + 32 byte

- <data\_range>

Define the address range in the target's RAM where the programming data is buffered for the programming algorithm.

64 byte argument buffer

buffer for programming data

256 byte stack

**Figure:** Memory mapping for the <data\_range>

The argument buffer used for the communication between the TRACE32 software and the programming algorithm is located at the first 64 bytes of <data\_range>. The 256 byte stack is located at the end of <data\_range>.

$<buffer\_size> = \text{size\_of}(<\text{data\_range}>) - 64 \text{ byte argument buffer} - 256 \text{ byte stack}$

$<buffer\_size>$  is the maximum number of bytes that are transferred from the TRACE32 software to the NAND Flash programming algorithm in one call.

- *<file>*

Lauterbach provides ready-to-run driver binary files for NAND Flash programming. They are located in the TRACE32 installation directory:

~~/demo/<architecture>/flash/<bus\_width>/

Where ~~ is expanded to the TRACE32 installation directory, which is c:/t32 by default.

For detailed information about how to determine the *<file>* parameter, see “[Identifying the Correct Driver Binary File for a NAND Flash Device](#)” on [page 26](#).

There are two ways to find the correct \*.bin file:

- You can identify the \*.bin file via our website, as described in this section.

- Alternatively, run a PRACTICE script (\*.cmm), as described in “[Finding the <nandflash\\_code> of a NAND Flash Device](#)”, page 29.

## To identify the correct \*.bin file:

1. For information about supported Flash devices, access the [Lauterbach](#) website.

2. Click the + tree button next to **Tool Chain**, and then click **Supported NAND/Serial Flash Controller** (<https://www.lauterbach.com/ylistnand.html>).

3. Open **Supported Flash Devices** in a separate window or tab (<https://www.lauterbach.com/ylist.html>).

4. On the **Supported Flash Devices** page, select the required company from the drop-down list.

Supported FLASH Devices

LAUTERBACH

Supported Flash Devices

NAND FLASH devices are marked in GREEN.

SERIAL FLASH devices are marked in RED.

5. Locate the desired Flash device.

You need the name of the Flash device to be able to identify the correct driver binary file.

6. Identify the correct \*.bin file based on the name of the Flash device. The following examples illustrate how to do this.

- [Examples for Generic NFCs](#)

- [Example for CPU-Specific NFCs](#)

- The file name convention for driver binary files (\*.bin) is explained [below](#).

## File Name Convention for NAND Flash Drivers

---

The NAND Flash drivers for the various NFC types use the following file name convention:

| Page Size (bytes) |            | Block Size | Device Size    | Bus Width | File Name       |

|-------------------|------------|------------|----------------|-----------|-----------------|

| Main area         | Spare area |            |                |           |                 |

| 512               | 16         | 32 pages   | <= 2048 blocks | 8         | Nand5608.bin    |

|                   |            |            |                | 16        | Nand5616.bin    |

| 512               | 16         | 32 pages   | > 2048 blocks  | 8         | Nand1208.bin    |

|                   |            |            |                | 16        | Nand1216.bin    |

| 2048              | 64         | 64 pages   | <= 1024 blocks | 8         | Nand1g08.bin    |

|                   |            |            |                | 16        | Nand1g16.bin    |

| 2048              | 64         | 64 pages   | > 1024 blocks  | 8         | Nand2g08.bin    |

|                   |            |            |                | 16        | Nand2g16.bin    |

| 2048              | 64         | 128 pages  | > 1024 blocks  | 8         | NandLAg08.bin   |

| 4096              | 128        | 64 pages   | > 1024 blocks  | 8         | Nand8g08.bin    |

| 4096              | 218        |            |                |           | Nand8g08xs.bin  |

| 4096              | 128        | 128 pages  | > 1024 blocks  | 8         | NandLBg08.bin   |

| 4096              | 218        |            |                |           | NandLBg08xs.bin |

“xs” = eXtra spare area

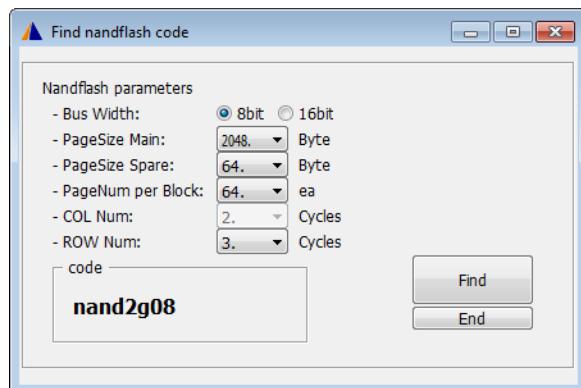

The following step-by-step procedure helps you find the <nandflash\_code> of your NAND Flash device. Based on the <nandflash\_code>, you can then identify the correct \*.bin file.

## To find the <nandflash\_code>:

1. Run the following PRACTICE script file (\*.cmm) from the TRACE32 demo folder:

```

CD.DO ~/demo/etc/flash/find_nanddef.cmm

```

```

;The path prefix ~ expands to the system directory of TRACE32,

;by default C:\t32.

```

If this demo script is missing, you can download it from [www.lauterbach.com/scripts.html](http://www.lauterbach.com/scripts.html).

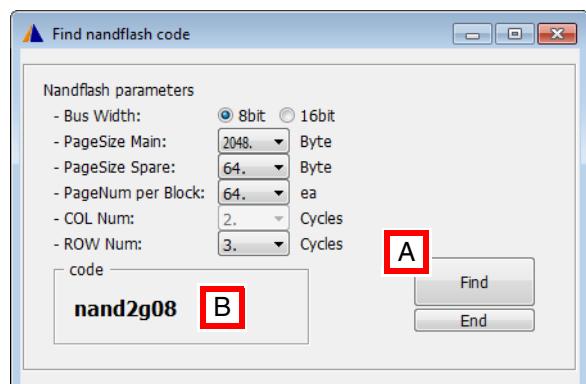

The **Find nandflash code** dialog opens.

2. Under **Nandflash parameters**, make your settings.

- You can find the required information in the NAND Flash data sheet of the manufacturer.

- The values selected in the screenshot are based on the [Illustration of a NAND Flash Array Organization](#).

3. Click **Find**.

- The **code** box displays the <nandflash\_code> of your NAND flash device.

- If the **code** box displays **unknown**, then proceed as described in "[If There is No Script](#)".

4. Make a note of the displayed <nandflash\_code>; for example, **nand2g08**.

5. Click **End** to close the **Find nandflash code** dialog.

6. Identify the correct \*.bin file based on the <nandflash\_code>. The following examples illustrate how to do this.

- [Examples for Generic NFCs](#)

- [Example for CPU-Specific NFCs](#)

## Illustration of a NAND Flash Array Organization

The terms highlighted in bold correspond to the drop-down lists and radio options of the **Find nandflash code** dialog box (below).

You can find the required information in the NAND Flash data sheet of the manufacturer.

|            | cycle | I/O7 | I/O6 | I/O5 | I/O4 | I/O3 | I/O2 | I/O1 | I/O0 |         |

|------------|-------|------|------|------|------|------|------|------|------|---------|

| Col. cycle | 1st   | CA7  | CA6  | CA5  | CA4  | CA3  | CA2  | CA1  | CA0  | COL Num |

|            | 2nd   | LOW  | LOW  | LOW  | LOW  | CA11 | CA10 | CA9  | CA8  |         |

| Row cycle  | 3rd   | RA19 | RA18 | RA17 | RA16 | RA15 | RA14 | RA13 | RA12 | ROW Num |

|            | 4th   | RA27 | RA26 | RA25 | RA24 | RA23 | RA22 | RA21 | RA20 |         |

|            | 5th   | LOW  | RA28 |         |

CA = Column address

RA = Row address

## “Find nandflash code” Dialog Box

[A] Once you have entered the information found in the NAND Flash data sheet of the manufacturer, click **Find**.

[B] The **type** box displays the `<nandflash_code>` of your NAND Flash device.

## Examples for Generic NFCs

The names of the required NAND Flash driver binary files consist of information from the **Controller** and/or **Code** columns. The following example illustrate how you can combine this information from the Lauterbach website to form the correct file name.

### Example 1 – target:

- CPU **S3C6410** with a generic NFC

- NAND Flash device **MT29F2G16**

The **Code** column identifies the name of the NAND Flash driver binary file: **nand2g16.bin**.

Note that the information in the **Controller** column is *not* part of the file name in this case.

| Samsung Semiconductor |            |         |  |

|-----------------------|------------|---------|--|

| CPU                   | CONTROLLER | COMMENT |  |

| S3C24XX               | generic    | NAND    |  |

| S3C6410               | s3c6410    | OneNAND |  |

| S3C6410               | s3c6410    | eMMC    |  |

| S3C64XX               | generic    | NAND    |  |

| Micron Technology, Inc. |         |          |             |   |

|-------------------------|---------|----------|-------------|---|

| TYPE                    | COMPANY | CODE     | COMMENT     |   |

| 28F00AM29EW             | MICRON  | M29EW    | 16-bit mode |   |

| 28F00AP30               | MICRON  | M29EWB   | 8-bit mode  |   |

| ⋮                       | ⋮       | ⋮        | ⋮           | ⋮ |

| MT29F1G16               | MICRON  | NAND1G16 | NAND Flash  |   |

| MT29F2G08               | MICRON  | NAND2G08 | NAND Flash  |   |

| MT29F2G16               | MICRON  | NAND2G16 | NAND Flash  |   |

| MT29F4G08               | MICRON  | NAND2G08 | NAND Flash  |   |

The number **16** in the file name indicates the bus width and the folder where the file resides, i.e. in the **word** folder.

The binary file resides in this folder: `~/demo/arm/flash/word`

Whereas `~~` is expanded to the TRACE32 installation directory, which is `c:/t32` by default.

## Example 2 – target:

- CPU **AT91SAM3U4** with a generic (cortexm3) NFC.

Remember that NFCs flagged like this in the **Controller** column—*generic (name)*—require binary files that are compiled with a special instruction set, here *Thumb2*; see figure below.

- NAND Flash device **MT29F2G08**

Taken together, the **Code** column and the **Controller** column make up the file name of this particular NAND Flash driver binary file: **nand2g08\_cortexm3.bin**

The number **8** in the file name indicates the bus width and the folder where the file resides, i.e. in the **word** folder.

The binary file resides in this folder: `~/demo/arm/flash/byte`

Where `~~` is expanded to the TRACE32 installation directory, which is `c:/t32` by default.

This results in the following command line:

```

; Specify the NAND Flash programming algorithm and where it runs in

; the target RAM.      <code_range>      <data_range>      <file>

FLASHFILE.TARGET 0x20000000+0x1fff 0x20002000++0x1fff

~/demo/arm/flash/byte/nand2g08_cortexm3.bin

```

## Example for CPU-Specific NFCs

### Target:

- CPU **i.MX31** with a CPU-specific controller

- NAND Flash device **MT29F2G16**

Taken together, the **Code** column and the **Controller** column make up the file name of the NAND Flash driver binary file: **nand2g16\_imx.bin**

The diagram illustrates the mapping of supported components from two tables. A red line connects the 'Supported NAND/Serial Flash Controller' checkbox in the Freescale table to the 'Supported Flash Devices' checkbox in the Micron table. Another red line connects the 'CODE' column in the Freescale table to the 'CODE' column in the Micron table, specifically highlighting the 'NAND2G16' entry.

| Freescale Semiconductor, Inc.       |         |            |           |

|-------------------------------------|---------|------------|-----------|

|                                     | CPU     | CONTROLLER | COMMENT   |

| <input type="checkbox"/>            | i.MX21  | imx        | NAND      |

| <input checked="" type="checkbox"/> | i.MX31  | imx        | NAND      |

| <input type="checkbox"/>            | i.MX31  | imx        | SPI(CSPI) |

| <input type="checkbox"/>            | i.MX35  | imx25      | NAND      |

| <input type="checkbox"/>            | i.MX35  | imx35      | SPI(CSPI) |

| <input type="checkbox"/>            | MPC5121 | mpc51xx    | NAND      |

| <input type="checkbox"/>            | MPC8313 | mpc83xx    | NAND      |

| <input type="checkbox"/>            | MPC8377 | mpc83xx    | NAND      |

| Micron Technology, Inc.             |              |         |           |                      |

|-------------------------------------|--------------|---------|-----------|----------------------|

|                                     | TYPE         | COMPANY | CODE      | COMMENT              |

| <input type="checkbox"/>            | 28F00AM29EW  | MICRON  | M29EW     | 16-bit mode          |

| <input type="checkbox"/>            | 28F00AM29EWB | MICRON  | M29EWB    | 8-bit mode           |

| <input type="checkbox"/>            | MT29F2G08    | MICRON  | NAND2G08  | NAND Flash           |

| <input checked="" type="checkbox"/> | MT29F2G16    | MICRON  | NAND2G16  | NAND Flash           |

| <input type="checkbox"/>            | MT29F4G08    | MICRON  | NAND2G08  | NAND Flash           |

| <input type="checkbox"/>            | MT29F4G16    | MICRON  | NAND2G16  | NAND Flash           |

| <input type="checkbox"/>            | MT29F8G08    | MICRON  | NAND2G08  | NAND Flash           |

| <input type="checkbox"/>            | MT29F8G08MAD | MICRON  | NAND8G08M | NAND Flash, 4KB/218B |

| <input type="checkbox"/>            | MT29F8G16    | MICRON  | NAND2G16  | NAND Flash           |

The number **16** indicates the bus width and the folder where the file resides, i.e. in the **word** folder.

The file resides in this folder: `~/demo/arm/flash/word`

Where `~~` is expanded to the TRACE32 installation directory, which is `c:/t32` by default.

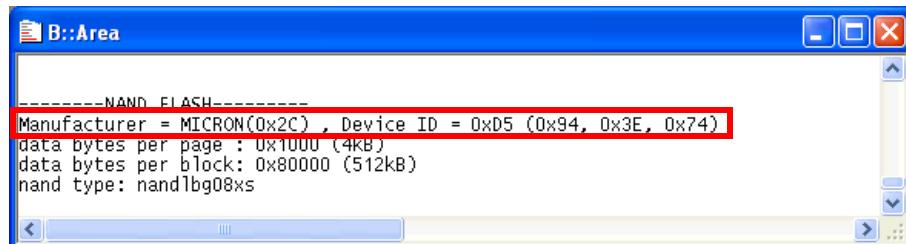

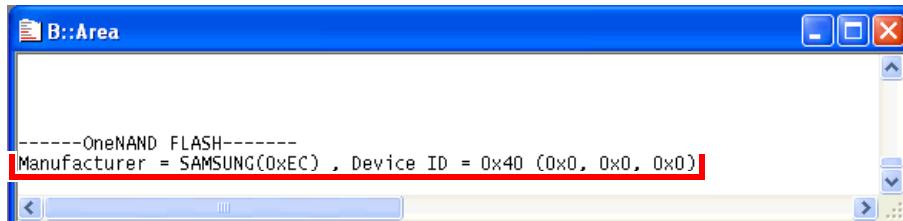

# Checking the Identification from the NAND Flash Device

The following command can be used to check if TRACE32 can access the NAND Flash device:

## **FLASHFILE.GETID**

Get the ID values, page size, block size, and the NAND Flash code from the NAND Flash device.

```

; Open the TRACE32 AREA window.

AREA.view

; Get the ID values, page size, block size, and the NAND Flash code

; from the NAND Flash device.

FLASHFILE.GETID

```

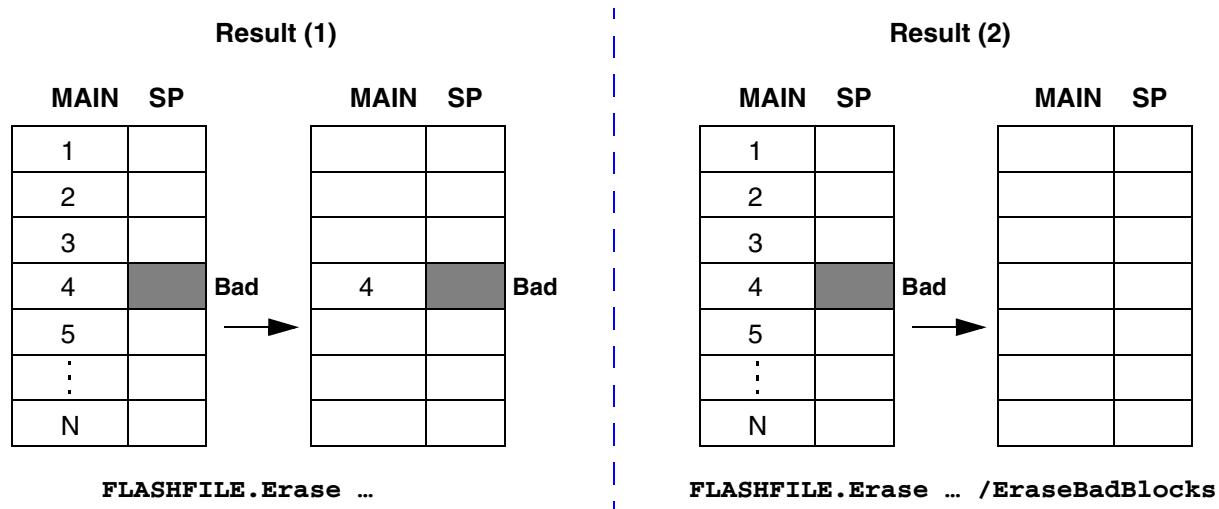

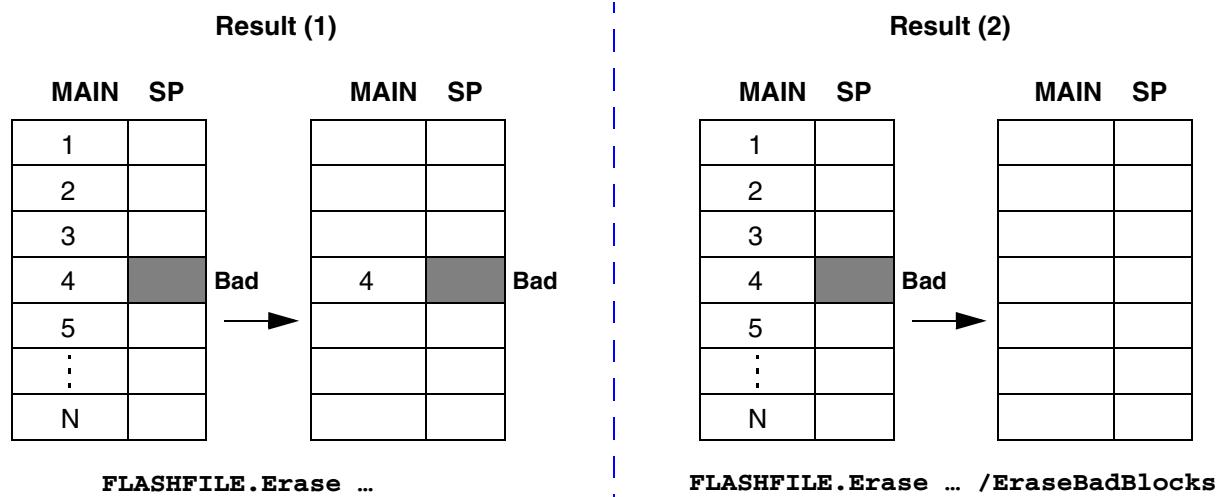

# Erasing the NAND Flash Device

The following commands are available to erase NAND Flash devices:

**FLASHFILE.Erase <range>**

Erase NAND Flash except bad blocks.

**FLASHFILE.Erase <range> /EraseBadBlocks**

Erase NAND Flash including bad blocks.

## Example 1:

```

; Erase 1MB starting from 0x0 except bad blocks.

FLASHFILE.Erase 0x0--0xFFFF

```

## Example 2:

```

; Erase 1MB starting from 0x0 including bad blocks.

; Afterwards all bad block data is erased.

FLASHFILE.Erase 0x0--0xFFFF /EraseBadBlocks

```

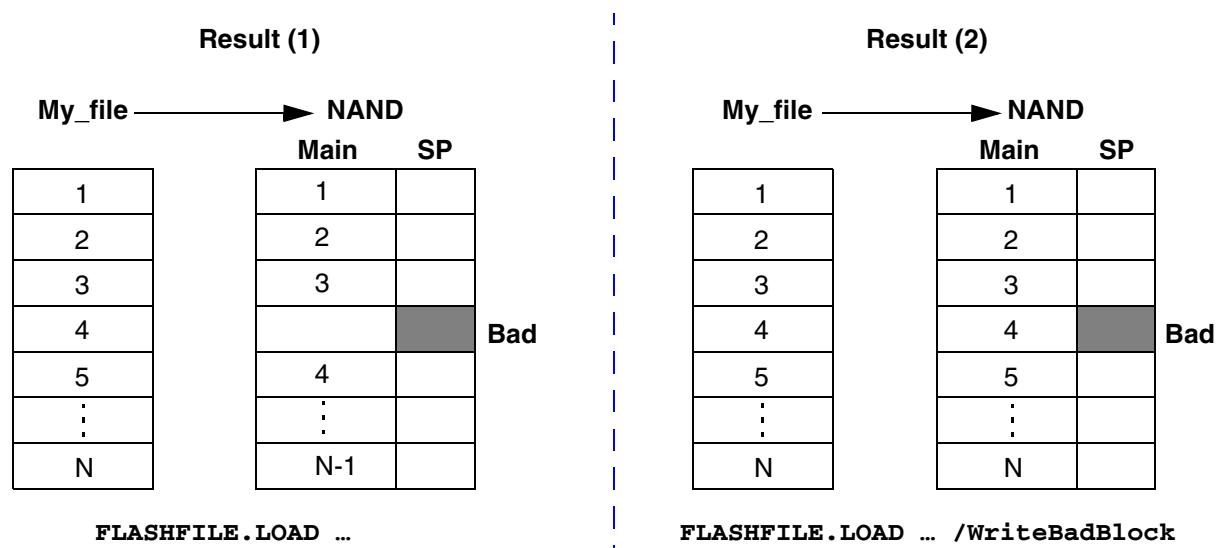

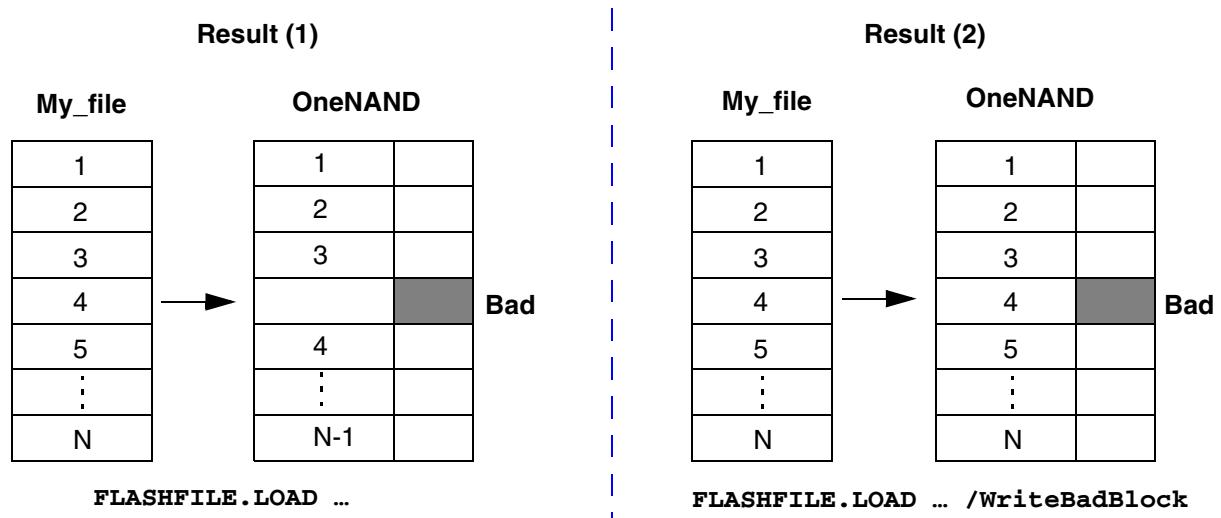

# Programming the NAND Flash Device

---

In a NAND Flash device, each page consists of two areas:

- The **main area** contains the data which is accessed by the CPU.

- The **spare area** contains the bad block information and the ECC data.

For background information about ECC, see “[Appendix: ECC \(Error Correction Code\)](#) on [page 80](#).

The main and spare area are programmed independently.

All CPU-specific NAND Flash controllers generate the ECC data automatically when data is programmed to the main area. Therefore, the spare area does not need to be programmed explicitly.

The following commands are available to program the NAND Flash main area:

**FLASHFILE.LOAD** <file> [<address> | <range>]

Program NAND Flash except bad blocks.

**FLASHFILE.LOAD** <file> [<address> | <range>] /WriteBadBlocks

Program NAND Flash including bad blocks.

The data from <file> is written to the address range specified by <range>. If no <range> or <address> is specified, programming starts at address 0x0. Currently only binary files can be programmed.

## Example 1

```

; Program contents of my_file.bin to NAND Flash main area starting at

; address 0x0.

; If a block is bad, the data is programmed to the next valid block.

FLASHFILE.LOAD my_file.bin 0x0--0xFFFF

```

## Example 2

```

; Program contents of my_file.bin to NAND Flash main area starting

; at address 0x0.

; Even if a block is bad, data will be programmed.

FLASHFILE.LOAD my_file.bin 0x0--0xFFFF /WriteBadBlock

```

The following command is used to compare the NAND Flash main area with the specified target file:

**FLASHFILE.LOAD <file> [<address> | <range>] /ComPare**

The data from <file> is compared to the address range specified by <range>. If no <range> or <address> is specified, comparing starts at address 0x0.

### Example 1

```

; Verify the contents of my_file.bin against the NAND Flash main area,

; starting at address 0x0.

; If a block is bad, then the data in the file is verified against

; the next valid block up to the end of the specified range.

FLASHFILE.LOAD my_file.bin 0x0--0xFFFF /ComPare

```

### Example 2

```

; Verify the contents of my_file.bin against NAND Flash main area,

; starting at address 0x0.

; Even if a block is bad, the data will be verified against the bad block

; data.

FLASHFILE.LOAD my_file.bin 0x0--0xFFFF /WriteBadBlock /ComPare

```

# Other Useful Commands (NAND)

## Writing Other File Formats to the Main Area

The following commands are available to load IntelHex and S-Record files:

**FLASHFILE.LOAD.IntelHex <file>**

Program an intelhex file to the NAND Flash.

**FLASHFILE.LOAD.S1record <file>**

**FLASHFILE.LOAD.S2record <file>**

**FLASHFILE.LOAD.S3record <file>**

Program an S-record file to the NAND Flash.

## Modifying the Main Area

The following command is available to modify the contents of the NAND Flash memory. The maximum range that one **FLASHFILE.Set** command can modify is only one block of the Flash memory. If you want to modify three blocks, you need three **FLASHFILE.Set** commands, etc. See below for an example.

**FLASHFILE.Set [<address> | <range>] %<format> <data>**

Modify the contents of the NAND Flash.

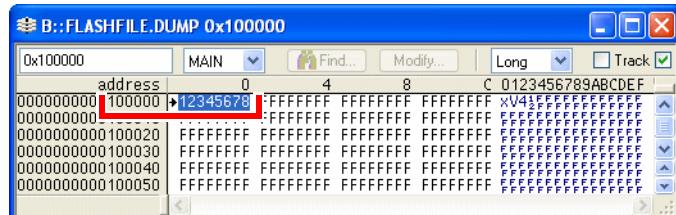

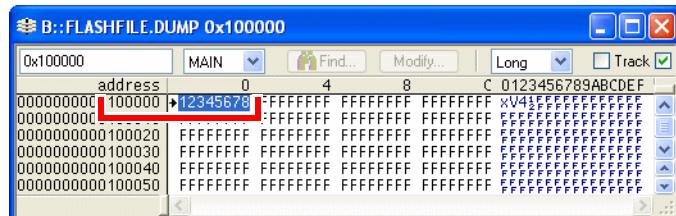

### Example 1

```

; Write 4 bytes of data 0x12345678 to the address 0x100000.

; LE = little endian

FLASHFILE.Set 0x100000 %LE %Long 0x12345678

```

### Result (1)

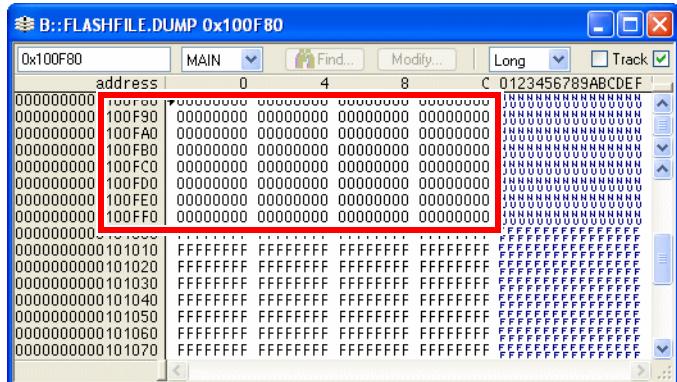

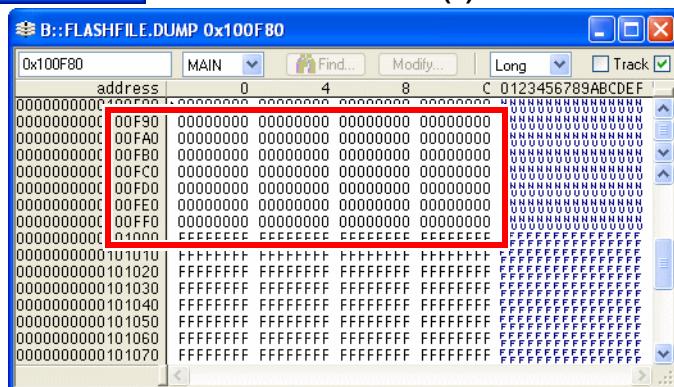

### Example 2

```

; Write data 0x0 to the address range 0x100000++0xFFFF.

FLASHFILE.Set 0x100000++0xFFFF %Byte 0x0

```

## Result (2)

### Example 3

```

; A NAND Flash has 128KB per block (0x20000).

; Write data 0x0 from 0x100000 to 0x15FFFF in the NAND Flash.

FLASHFILE.Set 0x100000++0xffff %Byte 0x0

FLASHFILE.Set 0x120000++0xffff %Byte 0x0

FLASHFILE.Set 0x140000++0xffff %Byte 0x0

```

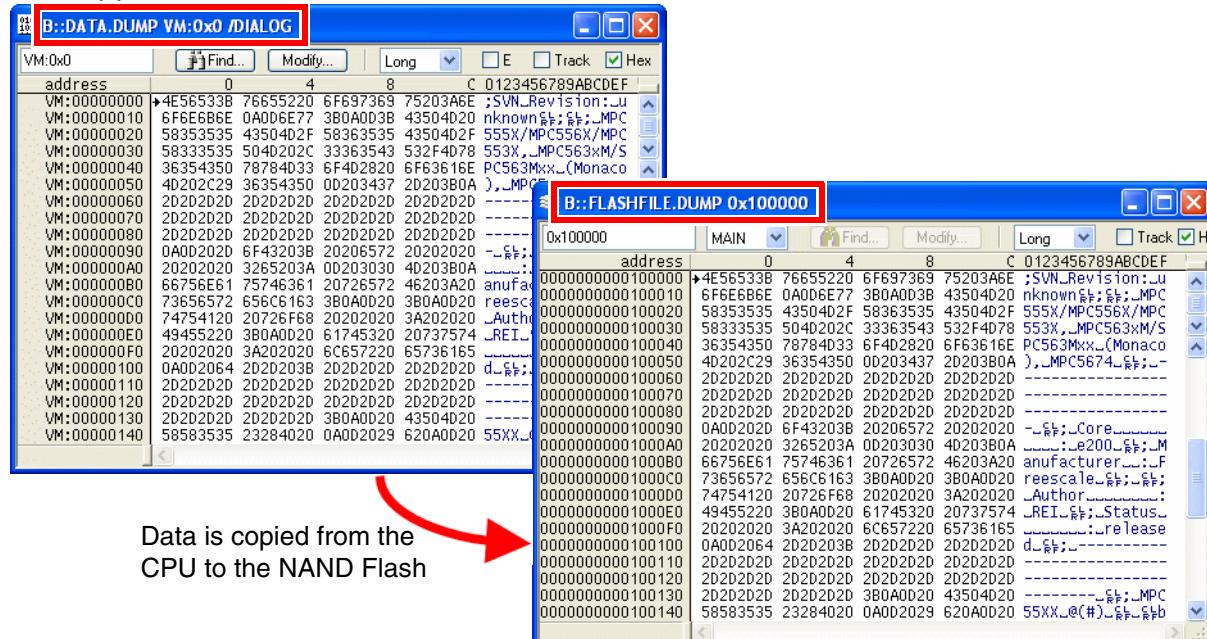

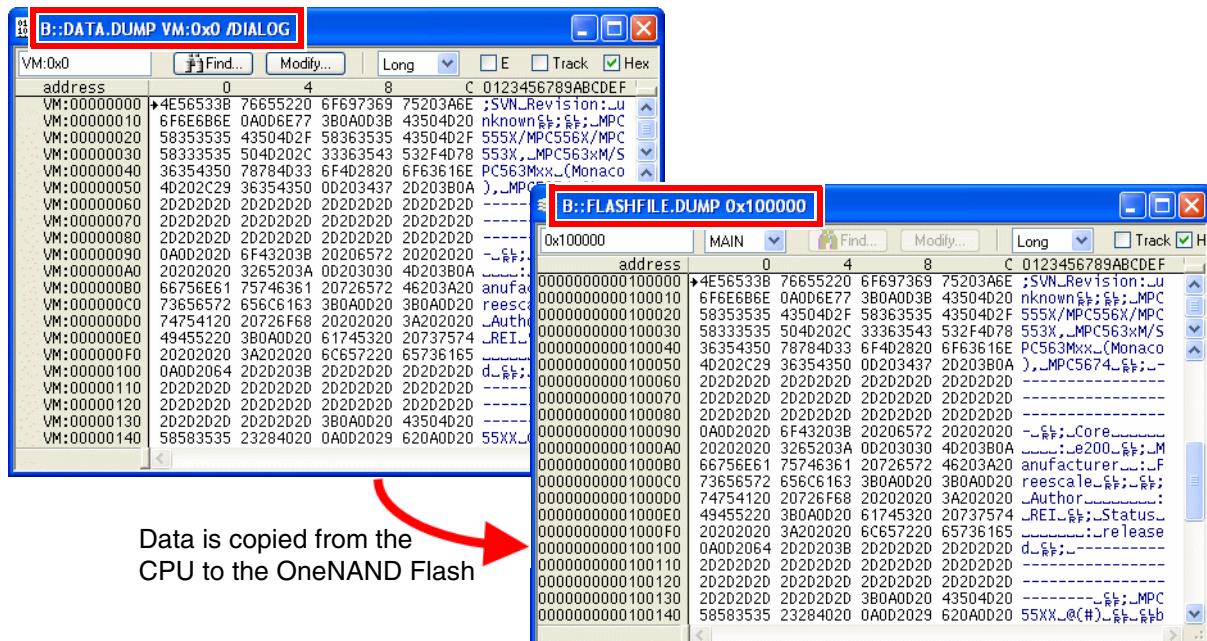

# Copying the Main Area

The following command is available to copy:

- Any data from any CPU memory area to the NAND Flash, or

- Any data from one address range of the NAND Flash to another address range within the same NAND Flash; for example, for backup purposes.

**FLASHFILE.COPY <source range> <target addr>**

Copy data from the source range to the defined address of the NAND Flash.

**FLASHFILE.COPY <source range> <target addr> /ComPare**

Verify the source range data against the target range data.

## Example 1

```

; Copy the 2MB virtual memory data at 0x0 to the NAND Flash address

; at 0x100000.

; Bad blocks are skipped, data is written to the next valid block.

; VM: The virtual memory of the TRACE32 software.

FLASHFILE.COPY VM:0x0--0xFFFFFFF 0x100000

```

## Result (1)

## Example 2

```

; Verify the data between virtual memory and NAND Flash.

```

```

FLASHFILE.COPY VM:0x0--0xFFFFFFF 0x100000 /ComPare

```

### Example 3

```

; Copy the 4MB NAND Flash data at 0x0 to the NAND Flash

; at 0x800000.

; Bad blocks are skipped, data is written to the next valid block.

FLASHFILE.COPY 0x0--0x3FFFFF 0x800000

; Verify the 4MB NAND Flash data between 0x0 and 0x800000.

FLASHFILE.COPY 0x0--0x3FFFFF 0x800000 /ComPare

```

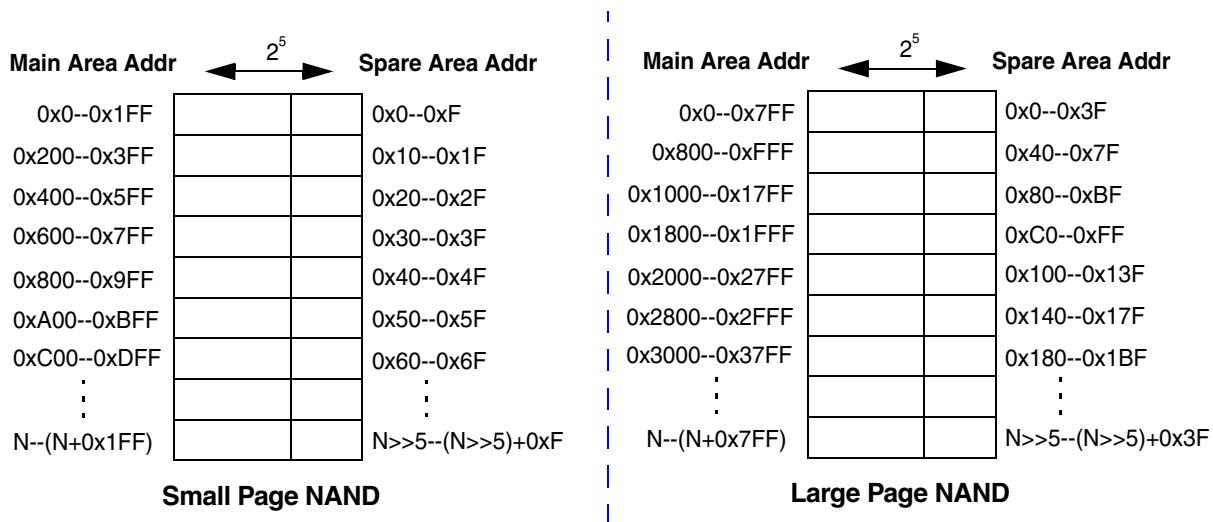

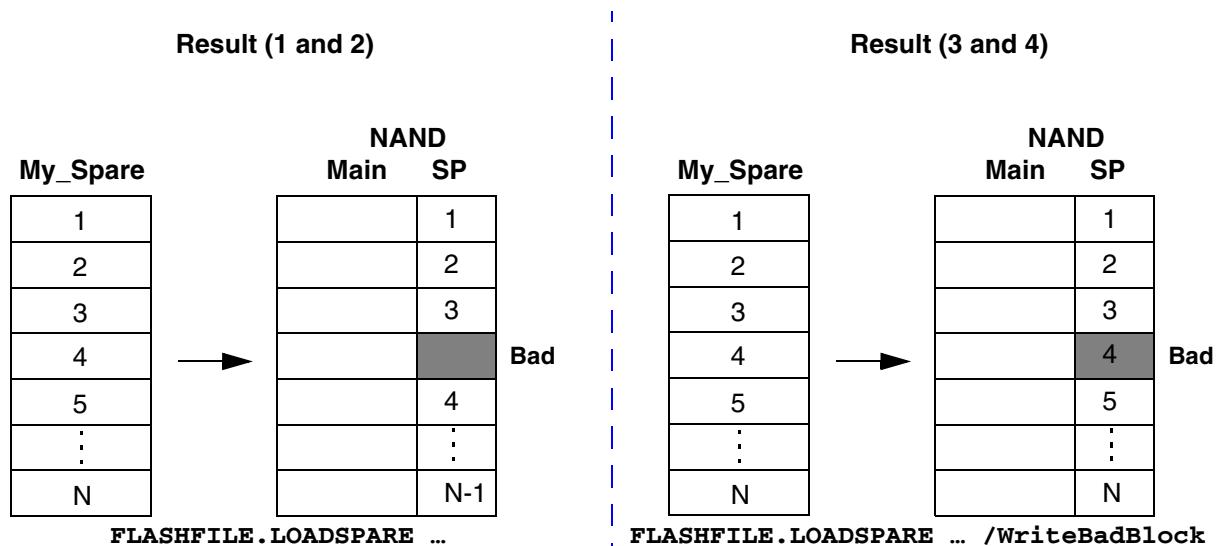

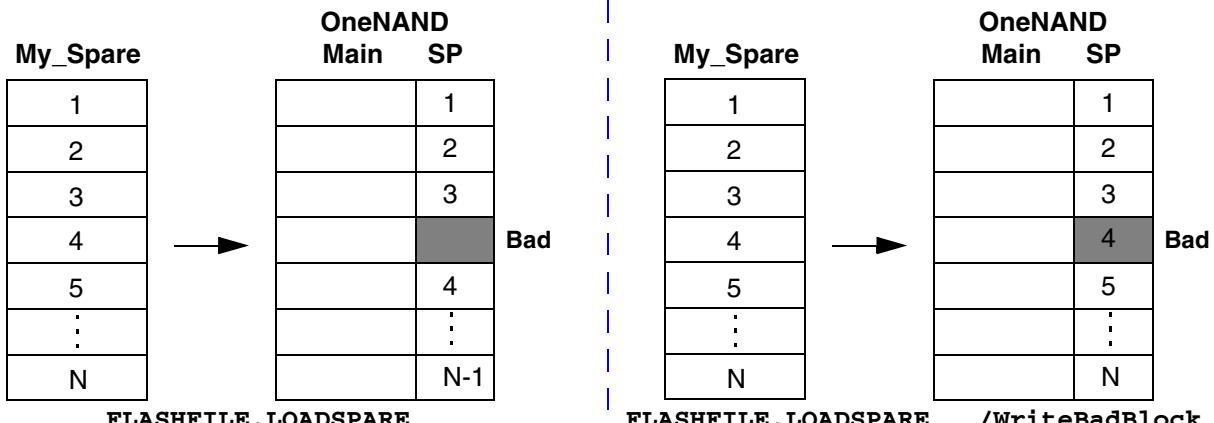

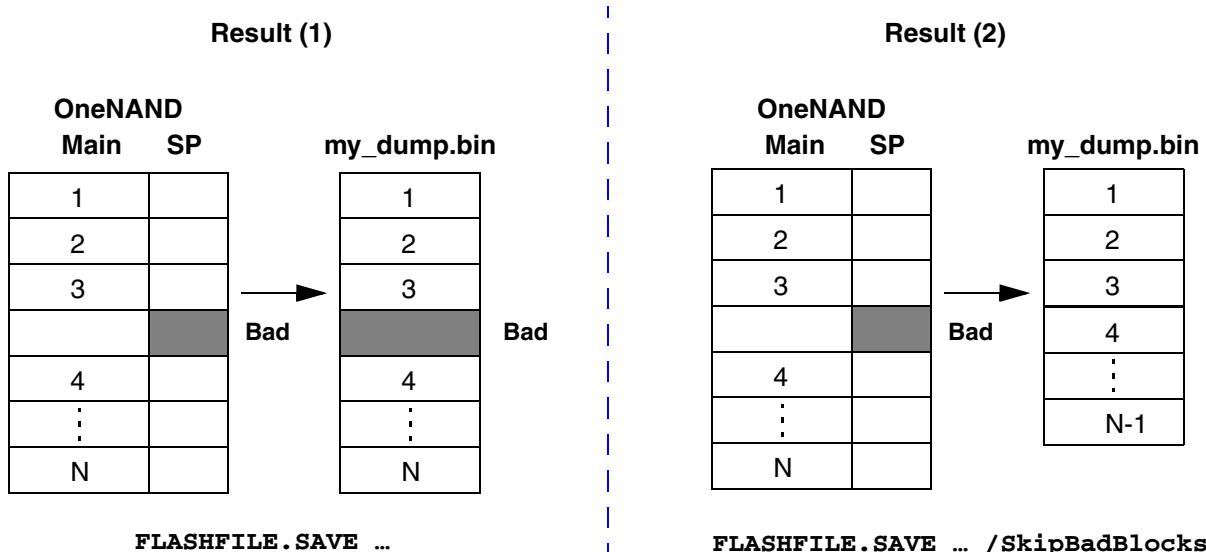

# Programming the Spare Area

The following commands are available to write a bad block marker, ECC codes, and special customer data to the NAND Flash spare area:

Program the NAND Flash spare area except bad blocks.

**FLASHFILE.LOADSPARE** <file> [<address> | <range>]

Program the NAND Flash spare area including bad blocks.

**FLASHFILE.LOADSPARE** <file> [<address> | <range>] /WriteBadBlocks

Compare the NAND Flash spare area except bad blocks.

**FLASHFILE.LOADSPARE** <file> [<address> | <range>] /ComPare

Compare the NAND Flash spare area including bad blocks.

**FLASHFILE.LOADSPARE** <file> [<address> | <range>] /WriteBadBlocks /ComPare

The data from <file> is written to the address range specified by <range>. If no <range> or <address> is specified, programming starts at address 0x0. Currently only binary files can be programmed.

**NOTE:**

- You need a third-party tool to create the spare file (<file>).

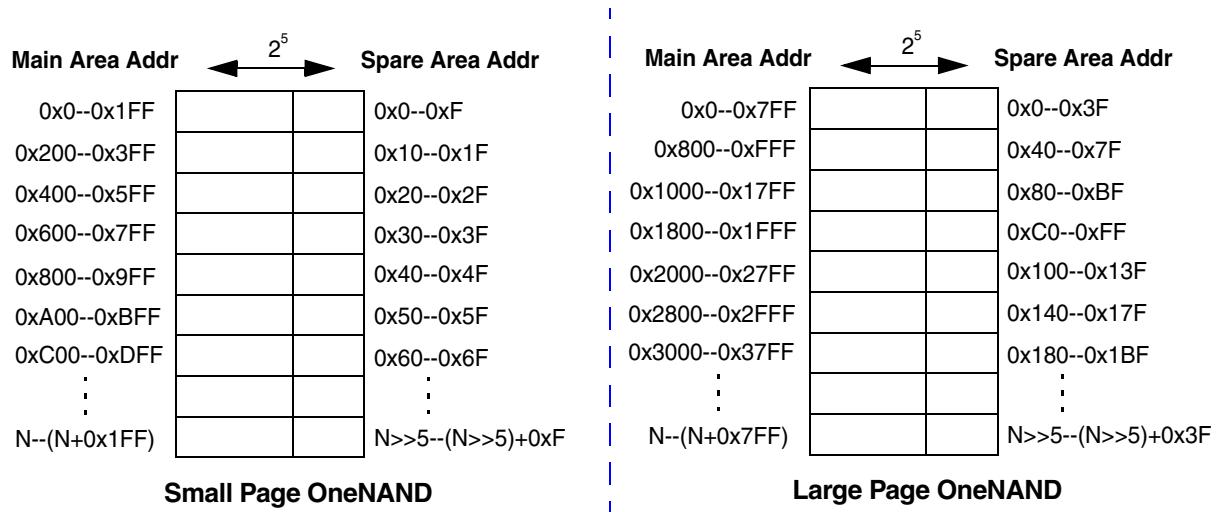

- Be careful when you specify <range>: You should input <range> in the spare area address format, not in the main area format (see figure below).

## Example 1

```

; Write my_spare.bin to the NAND Flash spare area.

; Start at the address 0x0 of the spare area.

; The bad blocks of my_spare.bin are excluded.

FLASHFILE.LOADSPARE my_spare.bin 0x0

```

## Example 2: When specifying the address range, remember to use the address format of the spare area.

```

; Write 32KB of my_spare.bin to the specified address range

; of the spare area.

; The bad blocks of my_spare.bin are excluded.

FLASHFILE.LOADSPARE my_spare.bin 0x0--0x7FFF

```

## Example 3

```

; Write my_spare.bin to the spare area.

; Start at the address 0x0 of the spare area.

; Include the bad blocks of my_spare.bin.

FLASHFILE.LOADSPARE my_spare.bin 0x0 /WriteBadBlock

```

## Example 4

```

; Write 32KB of my_spare.bin to the spare area.

; Start at the address 0x0 of the spare area.

; Include the bad blocks of my_spare.bin.

FLASHFILE.LOADSPARE my_spare.bin 0x0--0x7FFF /WriteBadBlock

```

## Example 5

```

; Verify the entire file my_spare.bin against the spare area.

; Start at the address 0x0 of the spare area.

FLASHFILE.LOADSPARE my_spare.bin 0x0 /ComPare

```

## Programming the ECC Code to the Spare Area

---

The following commands are available to generate ECC code file from the NAND Flash main area:

|                                      |                                                     |

|--------------------------------------|-----------------------------------------------------|

| <b>FLASHFILE.SAVEECC.BCH</b>         | Save error correction code (ECC) with BCH algorithm |

| <b>FLASHFILE.SAVEECC.hamming</b>     | Save ECC with Hamming algorithm                     |

| <b>FLASHFILE.SAVEECC.ReedSolomon</b> | Save ECC with Reed-Solomon algorithm                |

The following command is available to program the generated ECC code file to the NAND Flash spare area:

|                                       |                             |

|---------------------------------------|-----------------------------|

| <b>FLASHFILE.LOADEXC &lt;file&gt;</b> | Load ECC file to spare area |

|---------------------------------------|-----------------------------|

# Reading/Saving the NAND Flash Device

The CPU cannot read NAND Flash devices directly. But TRACE32 provides special commands for reading NAND Flash memories. The contents of the NAND Flash are displayed in a window.

## Reading the Main/Spare Area

The following commands are provided to read the NAND Flash areas.

**FLASHFILE.DUMP** [<address>] [/<format>]

Display a hex-dump of the NAND Flash main area.

**FLASHFILE.DUMP** [<address>] /SPARE [/Track]

Display a hex-dump of the NAND Flash spare area.

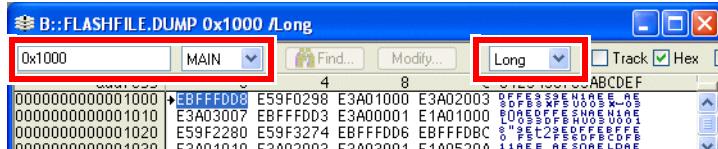

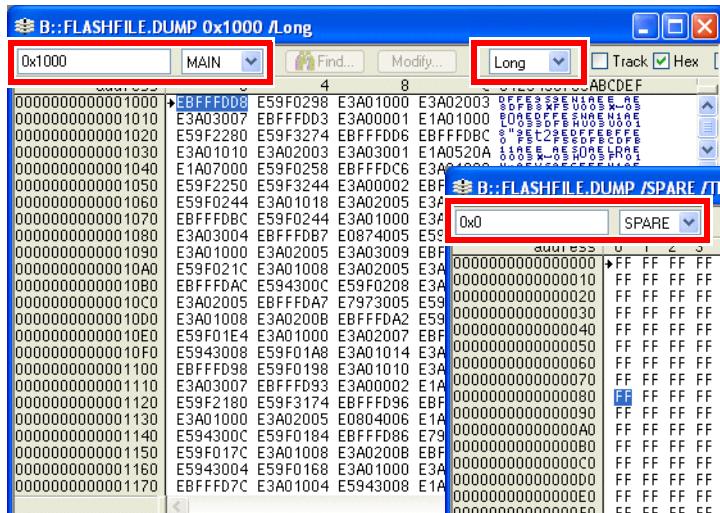

### Example 1

```

; Display a hex-dump of the NAND Flash main area starting at 0x1000.

; Display the information in a 32-bit format (Long option).

FLASHFILE.DUMP 0x1000 /Long

```

### Example 2

```

; Display a hex-dump of the NAND Flash spare area.

; The cursor in the spare area display follows the cursor movements in

; the main area display (Track option).

FLASHFILE.DUMP /SPARE /Track

```

### Result (1)

Result (2)

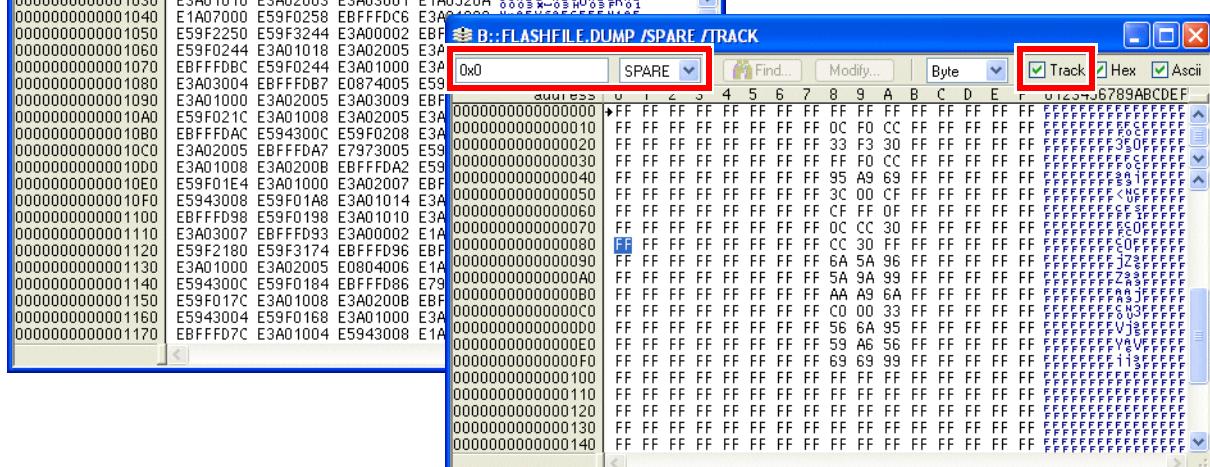

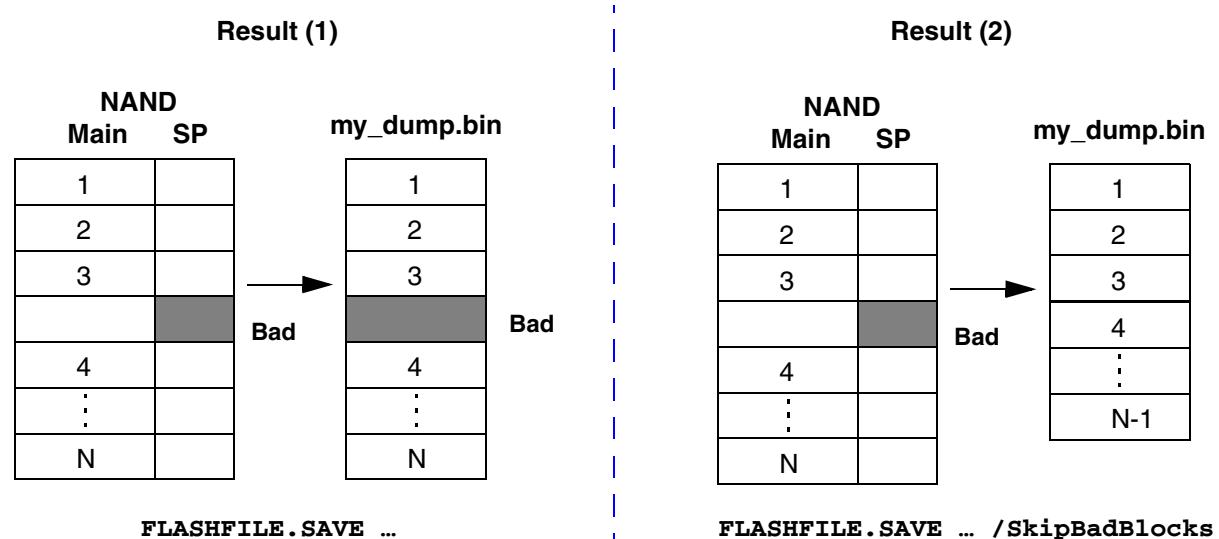

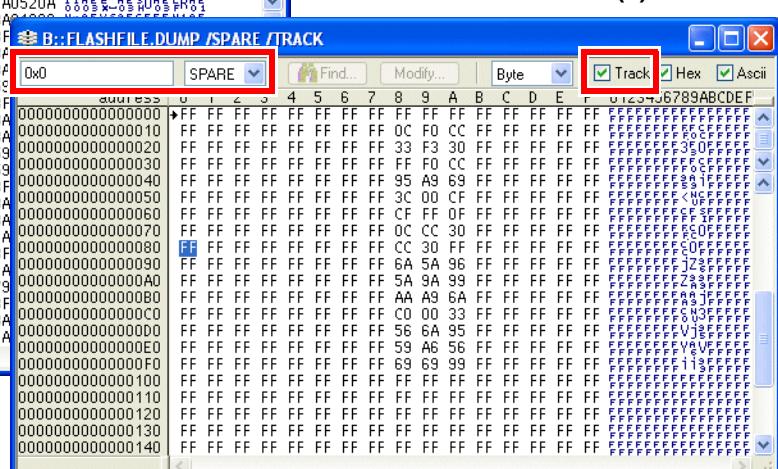

The following commands are available to save the contents of the NAND Flash main area to a file.

**FLASHFILE.SAVE** <file> <range>

Save the contents of the NAND Flash main area into <file>, bad blocks are saved.

**FLASHFILE.SAVE** <file> <range> /SkipBadBlocks

Save the contents of the NAND Flash main area into <file>, bad blocks are skipped.

### Example 1

```

; Save 1MB of the NAND Flash main area starting at 0x0 to the file

; my_dump.bin.

; The contents of bad block are also saved.

FLASHFILE.SAVE my_dump.bin 0x0--0xFFFF

```

### Example 2

```

; Save 1MB of the NAND Flash main area starting at 0x0 to the file

; my_dump.bin.

; The contents of bad block are skipped.

FLASHFILE.SAVE my_dump.bin 0x0--0xFFFF /SkipBadBlocks

```

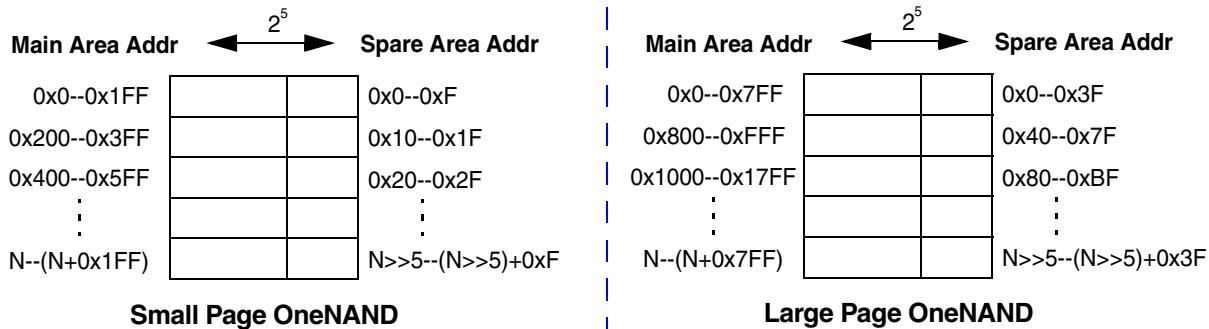

The following commands are available to save the contents of the NAND Flash spare area to a file.

**FLASHFILE.SAVESPARE** <file> <range>

Save the contents of the NAND Flash spare area into <file>, bad blocks are saved.

**FLASHFILE.SAVESPARE** <file> <range> /SkipBadBlocks

Save the contents of the NAND Flash spare area into <file>, bad blocks are skipped.

Please be careful when you specify <range>: You should input <range> in the spare area address format, not in the main area format (see figure below).

### Example 1

```

; Save 32KB of the NAND Flash spare area starting at 0x0 to the file

; my_dump_spare.bin.

; The contents of bad block are also saved.

FLASHFILE.SAVESPARE my_dump_spare.bin 0x0--0x7FFF

```

### Example 2

```

; Save 32KB of the NAND Flash spare area starting at 0x0 to the file

; my_dump_spare.bin.

; The contents of bad block are skipped.

FLASHFILE.SAVESPARE my_dump_spare.bin 0x0--0x7FFF /SkipBadBlocks

```

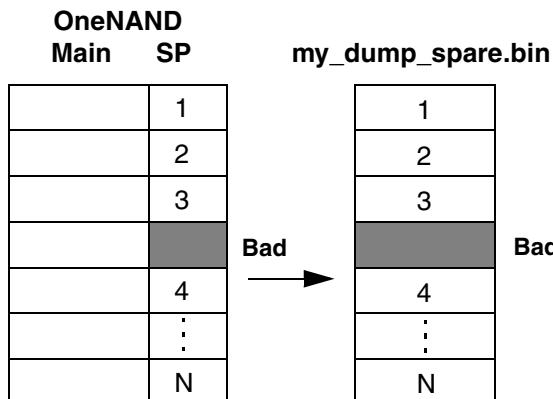

**Result (1)**

| NAND |     | my_dump_spare.bin |

|------|-----|-------------------|

| Main | SP  |                   |

|      | 1   |                   |

|      | 2   |                   |

|      | 3   |                   |

|      | Bad | Bad               |

|      | 4   |                   |

|      | ⋮   |                   |

|      | N   |                   |

**FLASHFILE.SAVESPARE ...**

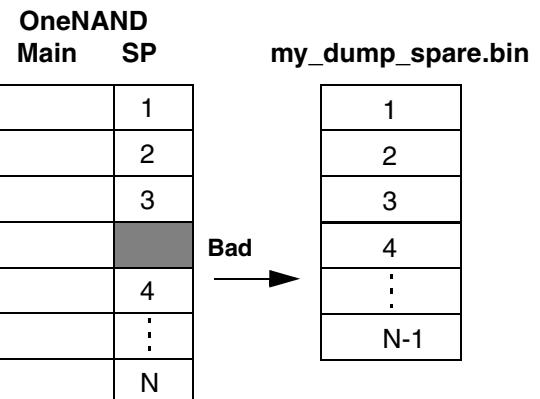

**Result (2)**

| NAND |     | my_dump_spare.bin |

|------|-----|-------------------|

| Main | SP  |                   |

|      | 1   |                   |

|      | 2   |                   |

|      | 3   |                   |

|      | Bad | Bad               |

|      | 4   |                   |

|      | ⋮   |                   |

|      | N-1 |                   |

**FLASHFILE.SAVESPARE ... /SkipBadBlocks**

## Example 1

CPU: OMAP3430 (Texas Instruments) based on an ARM11 core.

NAND Flash: MT29F1G08ABA (Micron)

NAND FLASH connected to the CS1 (Chip Selection 1) pin

Internal SRAM: 0x40200000

<cmd\_reg>: 0x6E0000AC

<addr\_reg>: 0x6E0000B0

<io\_reg>: 0x6E0000B4

```

; Select OMAP3430 as target CPU.

SYStem.CPU OMAP3430

; Establish the communication between the debugger and the target CPU.

SYStem.Up

; Disable watchdog.

DO disable_watchdog.cmm

; Enable CS1 and define the base address of CS1(NAND Flash).

; LE = little endian

PER.Set SD:0x6E0000A8 %LE %Long 0x870

; Define the NAND Flash access timing.

PER.Set SD:0x6E000098 %LE %Long 0x60401

PER.Set SD:0x6E00009C %LE %Long 0x05010801

; Define CS1 for 8 bit NAND Flash.

PER.Set SD:0x6E000090 %LE %Long 0x0800 ; GPMC_CONFIG1_1

; Disable write protection for the NAND Flash device.

PER.Set SD:0x6E000050 %LE %Long 0x10 ; GPMC_CONFIG

; Reset the Flash declaration within TRACE32.

FLASHFILE.RESet

; Inform TRACE32 about the NAND Flash register addresses.

FLASHFILE.Config 0x6E0000AC 0x6E0000B0 0x6E0000B4

; Specify the NAND Flash programming algorithm and where it runs in the

; target RAM.

FLASHFILE.TARGET 0x40200000++0x3fff 0x40204000++0x3fff

~/demo/arm/flash/byte/nand1g08.bin

; Check NAND Flash ID value.

FLASHFILE.GETID

```

```

; Erase NAND Flash including bad block.

FLASHFILE.ERASE 0x0--0xFFFF /EraseBadBlocks

; Program my_file.bin to NAND Flash main area.

FLASHFILE.LOAD my_file.bin 0x0--0xFFFFFFF

ENDDO

```

## Example 2

---

|                                                 |                                                                                                                                                       |

|-------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPU:                                            | The STM32F103 is based on a Cortex-M3 core, which only runs Thumb-2 code. For this reason, a NAND Flash programming driver in thumb code is required. |

| NAND Flash:                                     | Numonyx NAND512W3A2C (512 bytes per page), lock supported                                                                                             |

| NAND Flash connect to FSMC_NCE2, NAND Flash I/O |                                                                                                                                                       |

| <i>&lt;cmd_reg&gt;</i> :                        | 0x70020000                                                                                                                                            |

| <i>&lt;addr_reg&gt;</i> :                       | 0x70010000                                                                                                                                            |

| <i>&lt;io_reg&gt;</i> :                         | 0x70000000                                                                                                                                            |

| Target RAM:                                     | 20 KB SRAM at 0x20000000                                                                                                                              |

```

; Select STM32F103 as target CPU.

SYStem.CPU STM32F103ZE

; Establish the communication between the debugger and the target CPU.

SYStem.Up

; Clock enable to use FSMC and GPIO group related with NAND Flash.

PER.Set SD:0x40021014 %Long 0x114 ; FSMC clock enable

PER.Set SD:0x40021018 %Long 000001E0 ; GPIOD, GPIOE, GPIOF, GPIOG enable

; GPIO configuration CLE, ALE, D0->D3, NOE, NWE and NCE2

; (Output 50Mhz AF_PP), NWAIT((input pull-up) NAND pin configuration

PER.Set SD:0x40011400 %Long 0xB8BB44BB ; GPIOD_CRL

PER.Set SD:0x40011404 %Long 0xBB4BB444 ; GPIOD_CRH

PER.Set SD:0x4001140C %Long 0x00000040 ; GPIOD_ODR pin6

; D4->D7 NAND pin configuration (output 50Mhz AF_PP)

PER.Set SD:0x40011800 %Long 0xB4444444 ; GPIOE

PER.Set SD:0x40011804 %Long 0x444444BBB ; GPIOE

; INT2 NAND pin configuration (input pull-up)

PER.Set SD:0x40012000 %Long 0x48444444 ; GPIOG pin6

PER.Set SD:0x4001200C %Long 0x00000040 ; GPIOG_ODR pin6

; memory timing register

PER.Set SD:0xA0000068 %Long 0x01020301 ; FSMC_PMEM2

PER.Set SD:0xA000006C %Long 0x01020301 ; FSMC_PATT2

; Define & enable NAND Flash, 512 byte per page, ECC enable,

; 8 bit data width.

PER.Set SD:0xA0000060 %Long 0x0002004E ; FSMC_PCR2

; Declarations for NAND Flash programming

FLASHFILE.RESet

FLASHFILE.CONFIG 0x70020000 0x70010000 0x70000000

FLASHFILE.TARGET 0x20000000++0x1fff 0x20002000++0x1fff

~~~~/demo/arm/flash/byte/nand1208_cortexm3.bin

; Unlock, erase and program.

FLASHFILE.GETID

FLASHFILE.UNLOCK 0x000000++0xFFFFFFF

FLASHFILE.Erase 0x0000++0xFFFFFFFF /EraseBadBlocks

FLASHFILE.LOAD my_main_file.bin

ENDDO

```

# Full Example: CPU-Specific NAND Flash Programming

---

CPU: i.MX31 (Freescale)

NAND Flash: MT29F1G08 (Micron)

NAND Flash connected to the NFCE (Flash Chip Enable) pin

<base\_address>: 0xB8000000

Target RAM: 16KB SRAM at 0x1FFFC000

```

; Select i.MX31 as target CPU and establish communication between

; debugger and i.MX31.

SYSTem.RESet

SYSTem.CPU MCIMX31

SYSTem.Option.ResBreak OFF

SYSTem.JtagClock RTCK

SYSTem.Up

; Declare the NAND Flash Controller.

&nand_ctrl_base_addr=0xB8000000

FLASHFILE.RESet

FLASHFILE.CONFIG &nand_ctrl_base_addr , ,

FLASHFILE.TARGET 0x1FFFC000++0x1FFF 0x1FFE000++0x1FFF

~~/demo/arm/flash/byte/nand1g08_imx.bin

; Erase and program.

FLASHFILE.GETID

FLASHFILE.Erase 0x0++0xFFFF /EraseBadBlocks

FLASHFILE.LOAD C:\T32\my_file.bin 0x0++0xFFFF

ENDDO

```

# About OneNAND Flash Devices

---

A OneNAND Flash is a special NAND Flash type:

- A OneNAND Flash has a NOR Flash programming interface between the CPU and the OneNAND.

- The NAND Flash controller logic is part of the OneNAND Flash, so the target CPU does not need an integrated NAND Flash controller.

**Figure:** OneNAND Flash Block Diagram

# Scripts for OneNAND Flash Devices

---

This chapter describes how to create scripts for OneNAND Flash programming.

The steps and the framework (see below) provide an overview of the process. They are described in detail in the following sections.

The following steps are necessary to create a new script:

1. Establish communication between debugger and target CPU.

2. Configure the OneNAND Flash bus.

3. Reset the NAND Flash environment in TRACE32 to its default values.

4. Inform TRACE32 about the OneNAND Flash address (Flash declaration).

5. Inform TRACE32 about the OneNAND Flash programming algorithm.

6. Check the identification from the OneNAND Flash device.

7. Erase the OneNAND Flash device.

8. Program the OneNAND Flash device.

The following framework can be used as base for OneNAND Flash programming:

```

; Establish the communication

; between the CPU and the TRACE32

; debugger.

; Configure the OneNAND Flash

; controller.

FLASHFILE.RESET                                ; Reset the OneNAND Flash

; declaration within TRACE32.

FLASHFILE.CONFIG ...                          ; Inform TRACE32 about the

; OneNAND Flash register addresses.

FLASHFILE.TARGET ...                          ; Specify the OneNAND Flash

; programming algorithm and where

; it runs in target RAM.

FLASHFILE.GETID                                ; Get the ID values of the OneNAND

; Flash.

FLASHFILE.Erase ...                            ; Erase the OneNAND Flash.

FLASHFILE.LOAD <main_file> ...           ; Program the file to the OneNAND

; Flash (main area).

```

An ellipsis (...) in the framework indicates that command parameters have been omitted here for space economy.

**NOTE:** The parametrization of **FLASHFILE.CONFIG** and **FLASHFILE.TARGET** requires expert knowledge.

A template script (\*.cmm) for OneNAND Flash programming is provided by Lauterbach. It can be found in the TRACE32 installation directory.

~~/demo/<architecture>/flash/onenand.cmm

Where ~~ is expanded to the TRACE32 installation directory, which is c:/t32 by default.

# Establishing Communication between Debugger and Target CPU

OneNAND Flash programming with TRACE32 requires that the communication between the debugger and the target CPU is established. The following commands are available to set up this communication:

**SYStem.CPU** <cpu>

Specify your target CPU.

**SYStem.Up**

Establish the communication between the debugger and the target CPU.

```

SYStem.CPU OMAP3430      ; Select OMAP3430 as target CPU.

```

```

SYStem.Up                ; Establish the communication between the

; debugger and the target CPU.

```

## Configuring the OneNAND Flash Bus

Programming an off-chip OneNAND Flash devices requires a proper initialization of the external bus interface. The following settings in the bus configuration might be necessary:

- Definition of the base address of the OneNAND Flash devices

- Definition of the size of the OneNAND Flash devices

- Definition of the data bus width that is used to access the OneNAND Flash devices

- Definition of the timing (number of wait states for the access to the OneNAND Flash devices)