# Establish Your Debug Session

# Establish Your Debug Session

---

**TRACE32 Online Help**

**TRACE32 Directory**

**TRACE32 Index**

|                                                            |                                                                                     |

|------------------------------------------------------------|-------------------------------------------------------------------------------------|

| <b>TRACE32 Debugger Getting Started</b> .....              |  |

| <b>Establish Your Debug Session</b> .....                  | 1                                                                                   |

| <b>History</b> .....                                       | 4                                                                                   |

| <b>Establish your Debug Session</b> .....                  | 5                                                                                   |

| Key TRACE32 Setup Commands                                 | 5                                                                                   |

| The PER.view/PER.Set Command                               | 5                                                                                   |

| The Data.LOAD Command                                      | 7                                                                                   |

| Debug Scenarios                                            | 9                                                                                   |

| <b>Establish the Debug Communication</b> .....             | 11                                                                                  |

| <b>Debug Scenario 1</b> .....                              | 17                                                                                  |

| Onchip/NOR Flash Programming                               | 18                                                                                  |

| The Flash Programming File                                 | 18                                                                                  |

| On-chip Flash Programming                                  | 19                                                                                  |

| Off-chip NOR Flash Programming                             | 24                                                                                  |

| Configure the TRACE32 OS Awareness                         | 35                                                                                  |

| <b>Debug Scenario 2</b> .....                              | 36                                                                                  |

| Typical Boot Sequence                                      | 36                                                                                  |

| Flash Programming (NAND/Serial/eMMC)                       | 41                                                                                  |

| The Flash Programming File and the Debug Symbol File       | 41                                                                                  |

| NAND Flash Programming (non-generic NAND Flash Controller) | 42                                                                                  |

| eMMC Flash Programming                                     | 54                                                                                  |

| Establish the Communication                                | 55                                                                                  |

| Load the Debug Symbols                                     | 55                                                                                  |

| <b>Debug Scenario 3</b> .....                              | 56                                                                                  |

| Run the Boot Loader                                        | 57                                                                                  |

| Load Application (and/or OS) Code and Debug Symbols        | 58                                                                                  |

| Load Debug Symbols only                                    | 58                                                                                  |

| Configure the TRACE32 OS Awareness                         | 58                                                                                  |

| Complete Setup Example                                     | 58                                                                                  |

| <b>Debug Scenario 4</b> .....                              | 59                                                                                  |

| Write a Script to Configure the Target                     | 60                                                                                  |

| Load Application (and/or OS) Code and Debug Symbols        | 60                                                                                  |

| Configure the TRACE32 OS Awareness                         | 60                                                                                  |

|                               |           |

|-------------------------------|-----------|

| <b>Start-Up Scripts .....</b> | <b>61</b> |

| Write a Start-Up Script       | 61        |

| Run a Start-up Script         | 62        |

| Automated Start-up Scripts    | 62        |

## History

---

16-Oct-2014 Initial version of the manual.

23-Jan-2020 Full revision of the manual.

# Establish your Debug Session

---

Before you can start debugging, you need to set up the debug environment. The necessary configurations depend significantly on the specific debug scenario.

## Key TRACE32 Setup Commands

---

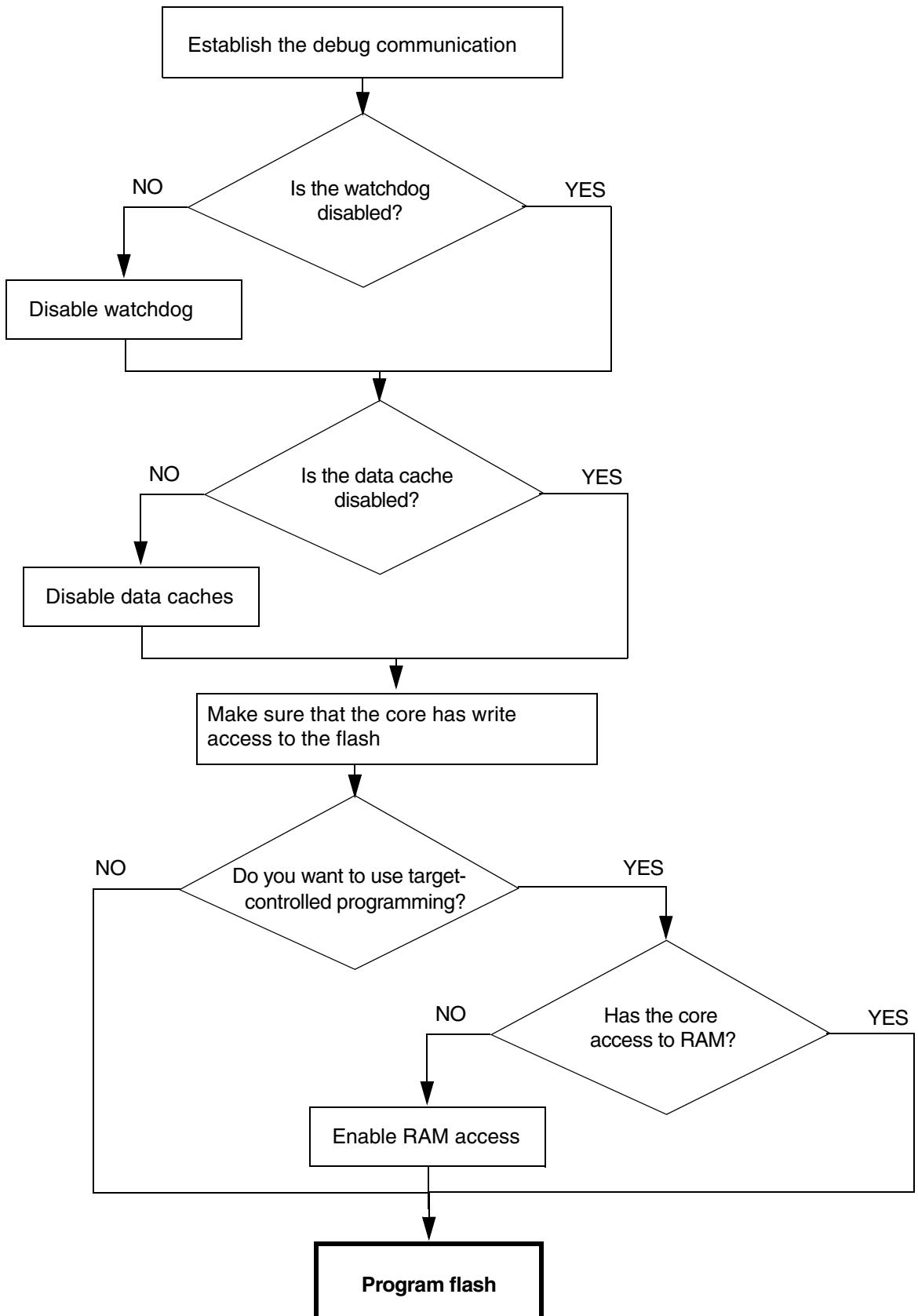

### The PER.view/PER.Set Command

---

A debug setup requires configuring various core/chip-related registers. The main commands to perform these configurations are:

**PER.Set.simple** <address>|<range> [%<format>] <string>

Modify configuration register/on-chip peripheral

**Data.Set** <address>|<range> [%<format>] <string>

Modify memory-mapped configuration register/on-chip peripheral

The main command to inspect the configurations is:

**PER.view** <file> [<tree\_search\_item>] /SpotLight

Display the configuration registers/on-chip peripherals, highlight changes

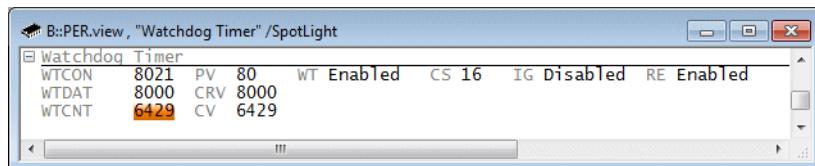

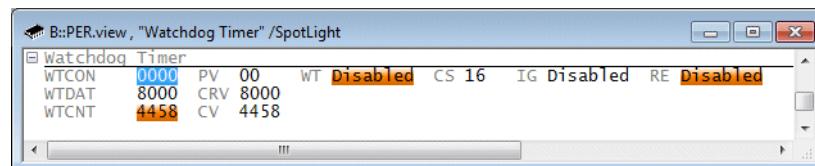

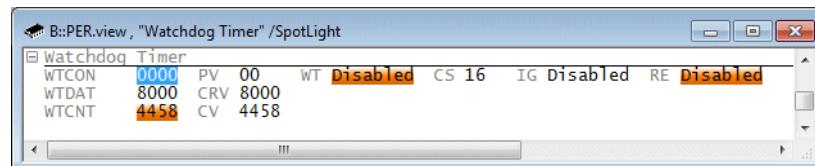

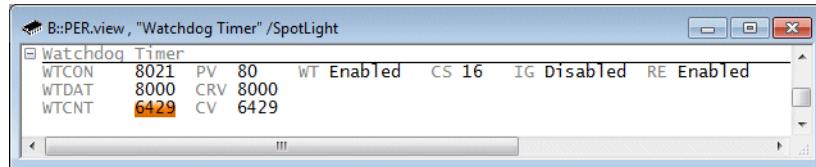

## Example: Disable Watchdog

```

; Display "Watchdog Timer" configuration registers, highlight changes

; a comma is used instead of the <file>

PER.view , "Watchdog Timer" /SpotLight

```

```

; Disable Watchdog timer by configuring Watchdog Timer Control Register

; (WTCN)

PER.Set.simple 0x53000000 %Long 0x0

```

Setting up a debug environment involves loading the code to be debugged and the associated debug symbols. TRACE32 PowerView supports a wide range of compilers and compiler output formats. You can find a list of supported compilers on the Lauterbach website.

The most important commands for loading the code to be debugged and the associated debug symbols are:

|                                                                       |                             |

|-----------------------------------------------------------------------|-----------------------------|

| <b>Data.LOAD.&lt;sub_cmd&gt; &lt;file&gt; /&lt;option&gt;</b>         | Load code and debug symbols |

| <b>Data.LOAD.Binary &lt;file&gt; /&lt;option&gt;</b>                  | Load only code              |

| <b>Data.LOAD.&lt;sub_cmd&gt; &lt;file&gt; /NoCODE /&lt;option&gt;</b> | Load only debug symbols     |

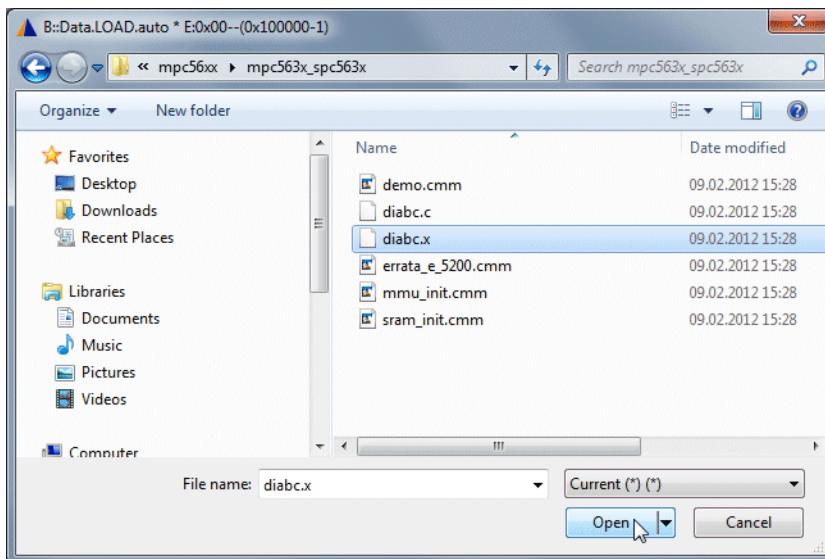

## Examples:

```

Data.LOAD.Elf demo-flash.elf          ; Load code and debug symbols from

; ELF file

Data.LOAD.AIF demo.axf                ; Load code and debug symbols from

; AIF file

Data.LOAD.Elf *                      ; Load code and debug symbols from

; ELF file

; open file browser to select file

Data.LOAD.Elf demo.elf /NoCODE        ; Load debug symbols from ELF file

Data.LOAD.Binary my_app.bin          ; Load code from binary file

```

A in-depth introduction to the **Data.LOAD** command is given in the chapter "["Load the Application Program"](#) (training\_hll.pdf).

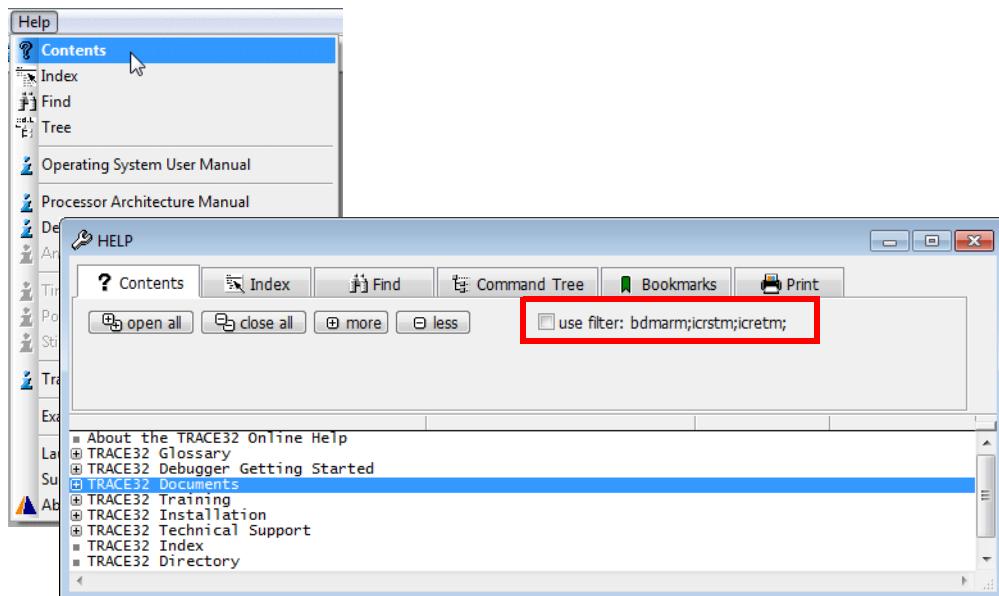

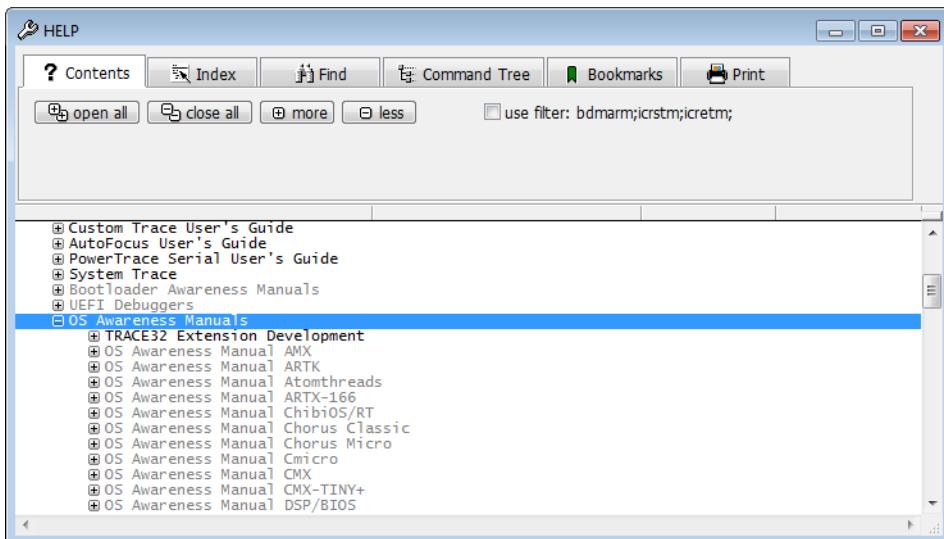

# The TASK.CONFIG Command

Today most applications use an operating system. TRACE32 PowerView includes a configurable target-OS debugger to provide symbolic debugging of operating systems.

Lauterbach provides ready-to-run configuration files for most common available OSes.

**To get the appropriate information on your OS, proceed as follows:**

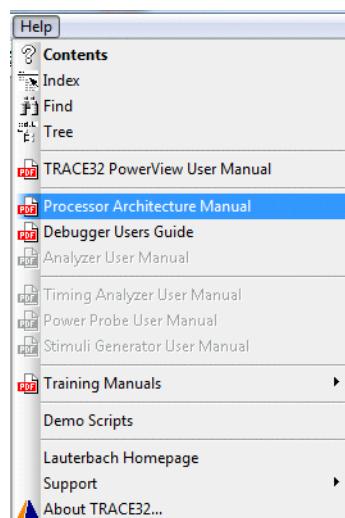

1. Open the online help and deactivate the help filter.

2. Open the TRACE32 **OS Awareness Manual** for your operating system.

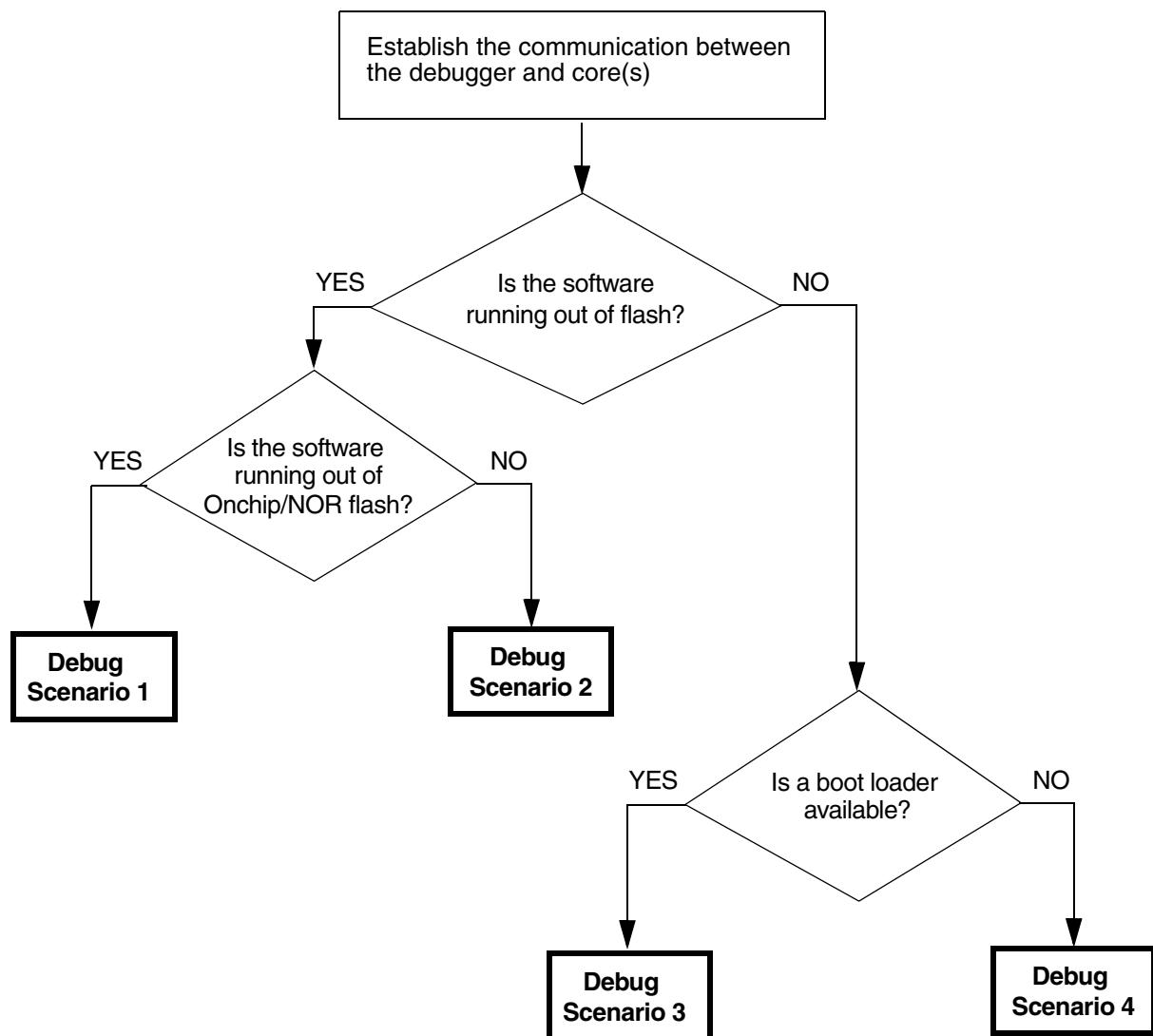

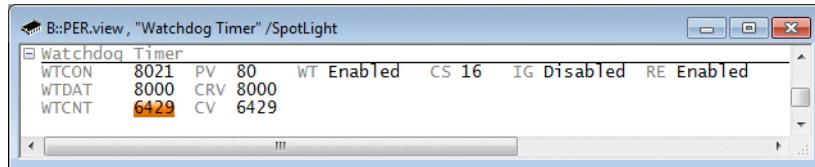

# Debug Scenarios

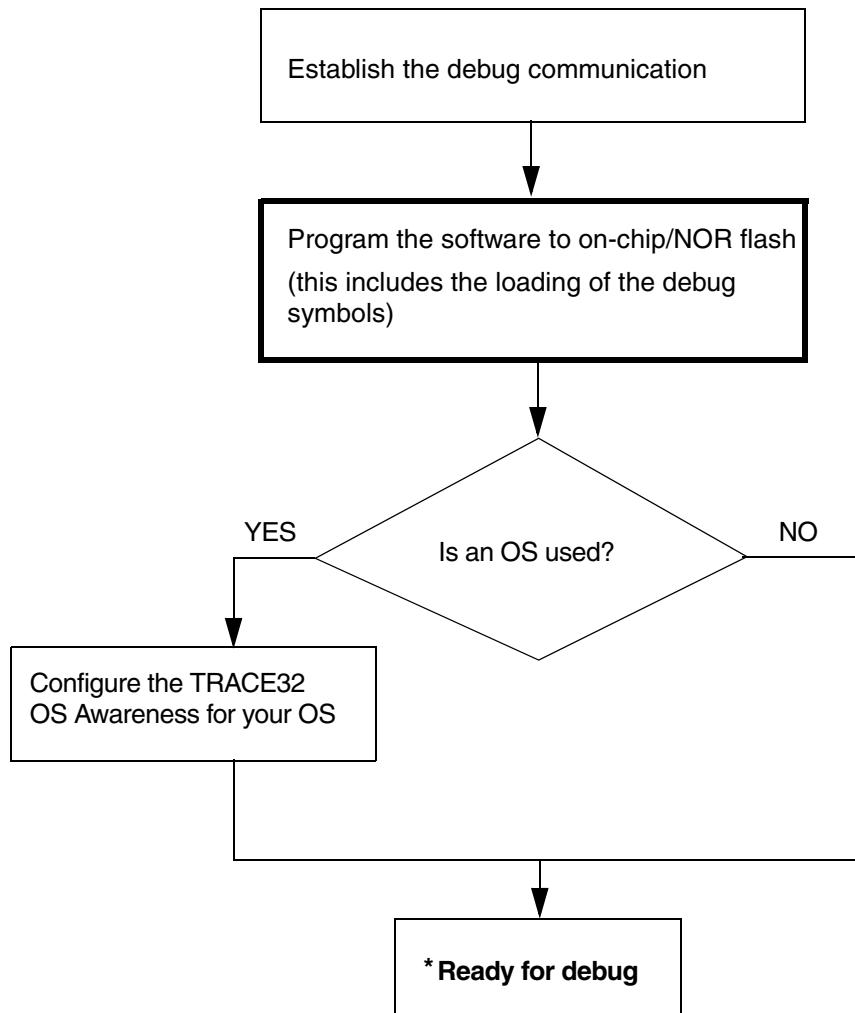

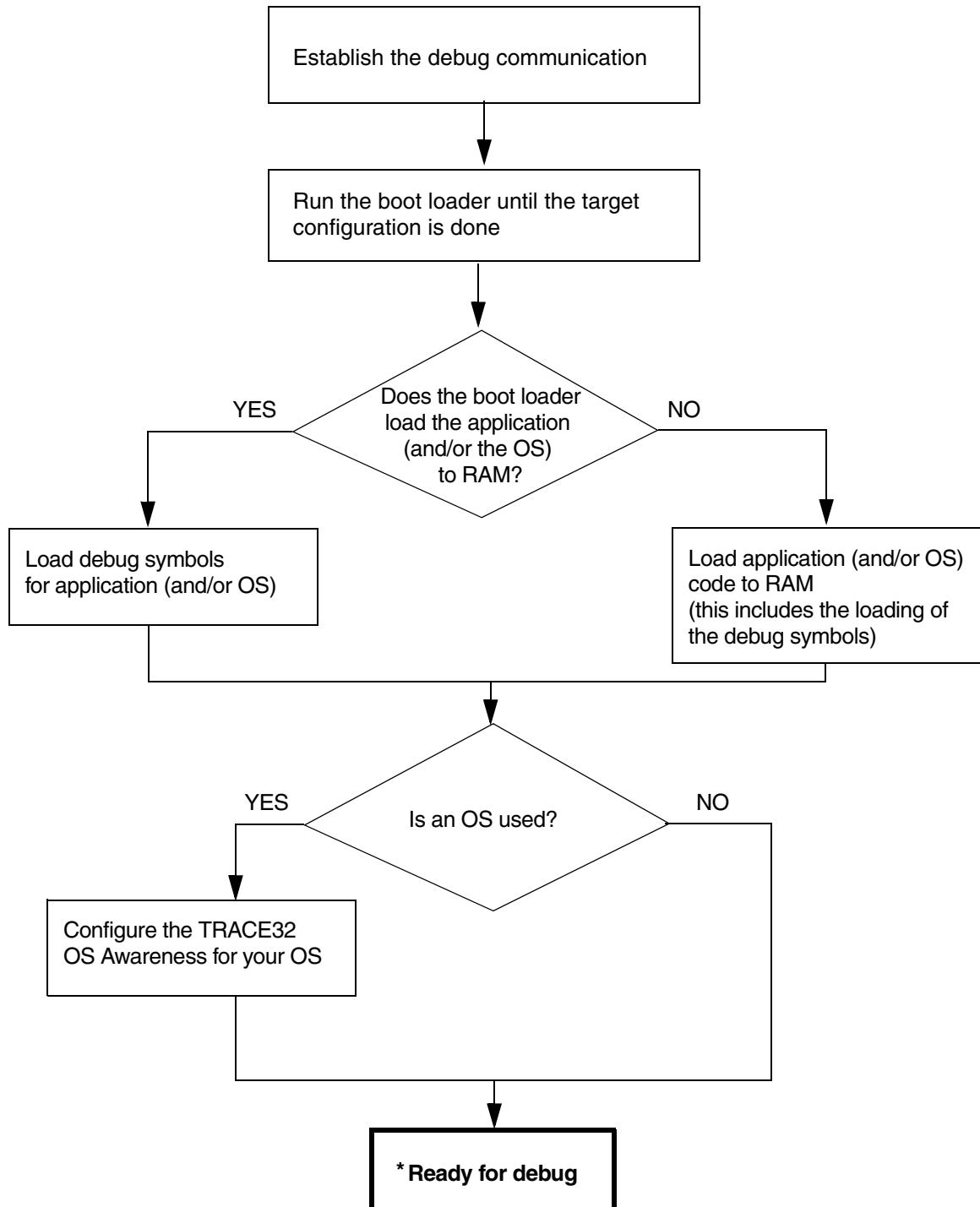

The necessary setup for your debug session depends crucially on the debug scenario. The graphic below shows you that there are mainly four debug scenarios.

After the communication between the debugger and the core(s) is established, there are four debug scenarios. Each debug scenario requires a different setup.

- **Debug Scenario 1**

The boot loader or the application (and/or the operating system) under debug is running out of Onchip/NOR flash.

- **Debug Scenario 2**

The boot loader under debug is running out of a flash e.g. a NAND or serial flash.

- **Debug Scenario 3**

The application (and/or the operating system) under debug are running out of RAM and a ready-to-run boot loader configures the target system and especially the RAM for this debug scenario.

- **Debug Scenario 4**

The application (and/or the operating system) under debug are running out of RAM. The target configuration, especially the RAM configuration has to be done by TRACE32 commands, because there is no ready-to-run boot loader.

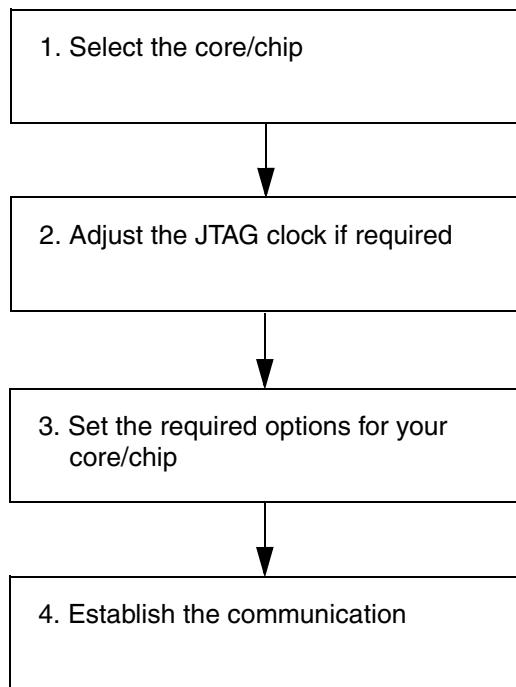

# Establish the Debug Communication

---

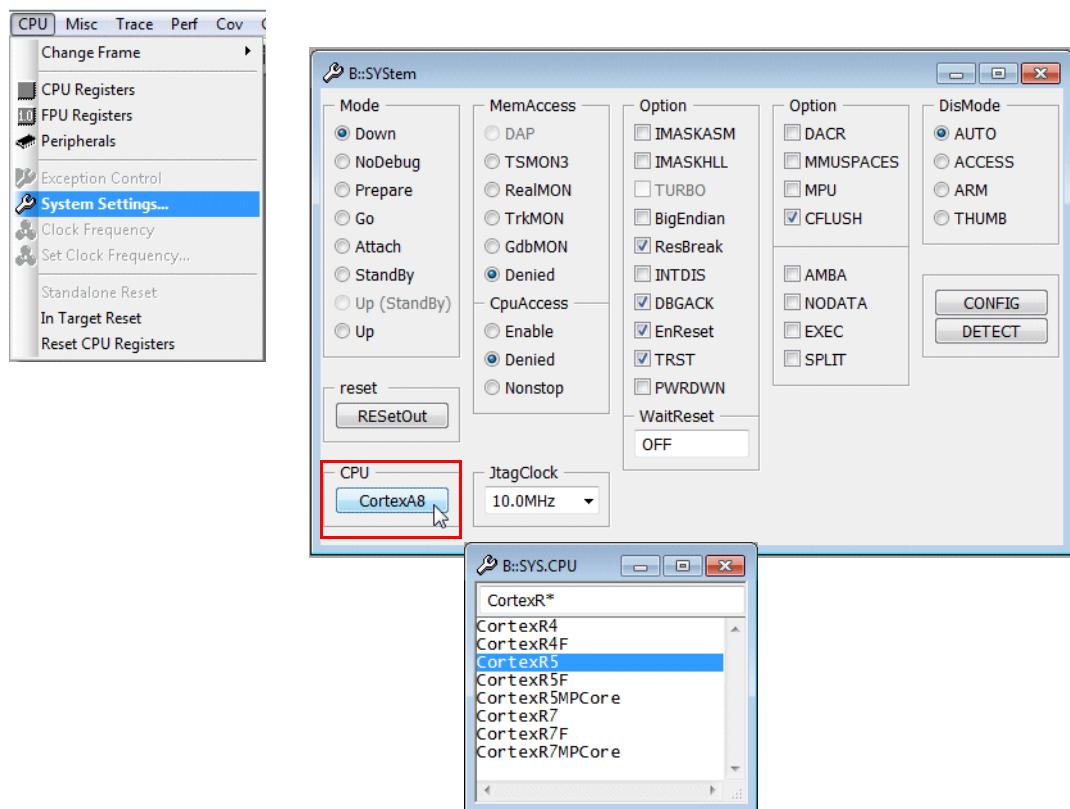

## 1. Select the target core/chip

Inform the debugger about the core/chip on your target, if an automatic detection of the core/chip is not possible. Wild card symbols \* or ? are allowed.

**SYStem.DETECT CPU**

Auto detection of CPU

**SYStem.CPU <cpu>**

Select the CPU/chip

```

SYStem.CPU CortexR5

```

```

SYStem.CPU CortexR5*

```

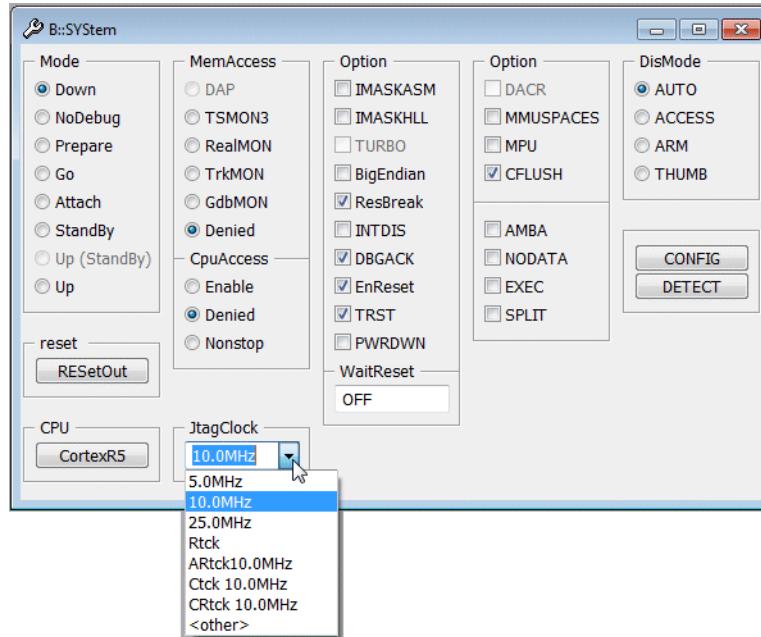

## 2. Adjust the JTAG clock

The debugger uses a default JTAG clock of 10 MHz. Adjusting the JTAG clock might be necessary:

- if a fixed relation between the core clock and the JTAG clock is specified.

**SYStem.JtagClock <frequency>**

Select the JTAG clock

```

SYStem.JtagClock 1.MHz

```

```

SYStem.JtagClock 100.kHz

```

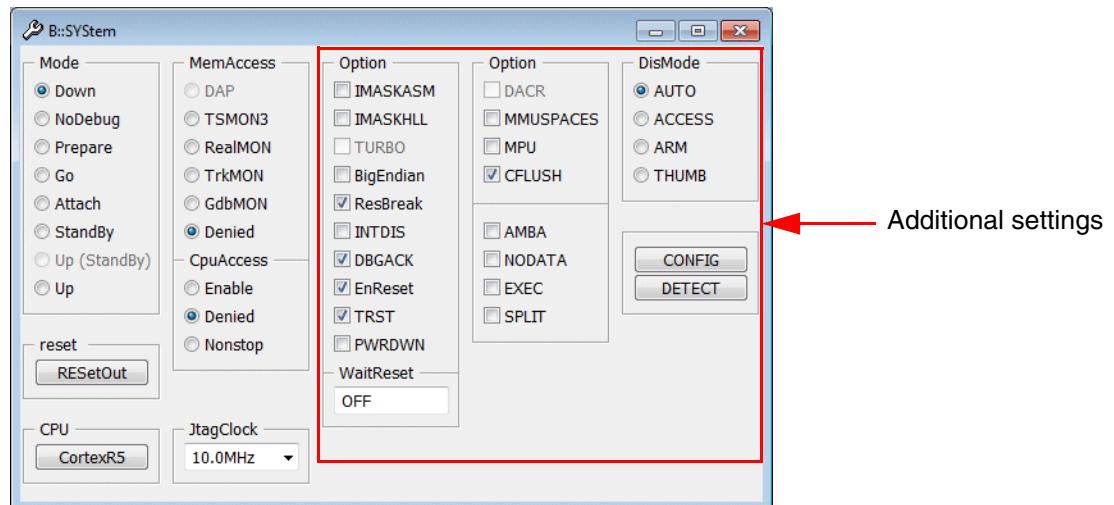

### 3. Set the required options for your core/chip

Some cores/chips require additional settings before the communication can be established.

For details refer to the **Processor Architecture Manual**.

#### 4. Establish the communication

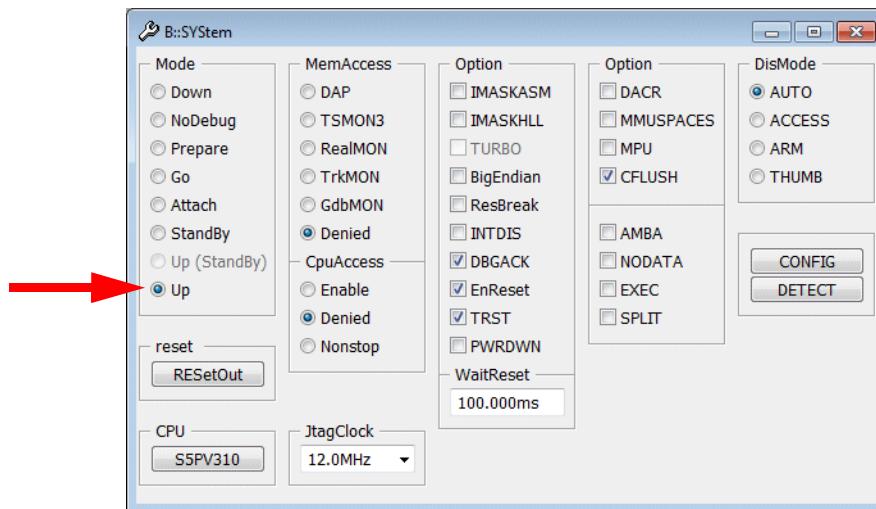

The most common way to establish the communication between the debugger and the core(s) is **Up**.

If **Up** is selected, the following steps are performed:

- Reset of the core/chip

- Initialization of the communication between the debugger and the core(s)

- Stop of the core(s) at the reset vector

#### SYStem.Up

Establish the communication between the debugger and the core(s)

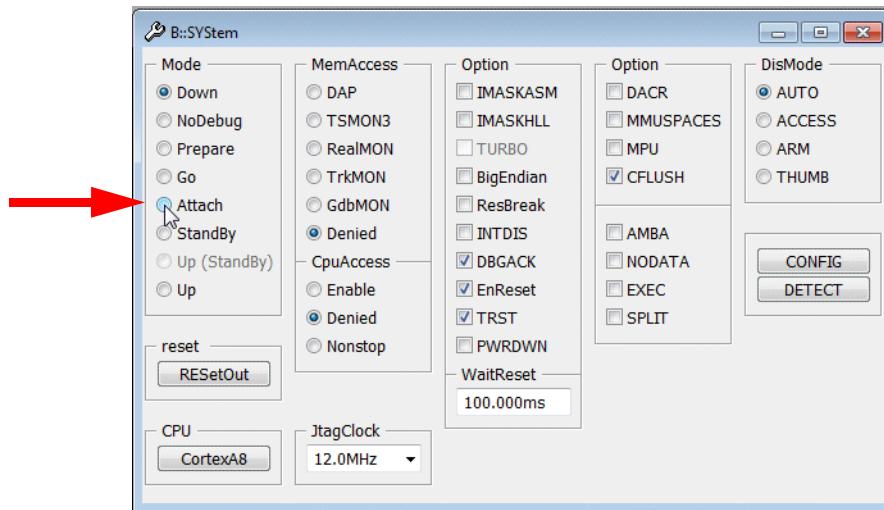

A second useful way to establish the communication between the debugger and the core/chip is **Attach**. **Attach** allows to connect the debugger to an already running core/chip.

If **Attach** is selected, the following step is performed:

1. Initialization of the communication between the debugger and the core(s).

#### SYStem.Mode Attach

Establish the communication between the debugger and the target core(s) (without reset)

SYStem.Mode Attach

Break ; stop the program execution

# Debug Scenario 1

The boot loader or the application (and/or the operating system) under debug is running out of the on-chip flash or out of a NOR flash device.

\*Considering the circumstance that a process has to be started manually e.g. via a TERMINAL window

# Onchip/NOR Flash Programming

---

The debugger supports the programming of on-chip flash and off-chip NOR flash devices.

**NOTE:** Flash programming requires that data cache is disabled for the address range covered by the FLASH.

## The Flash Programming File

---

On-chip flash and off-chip NOR flash programming allows to load any output file generated by your compiler.

Videos about the on-chip flash programming can be found here:

[support.lauterbach.com/kb/articles/flash-programming](https://support.lauterbach.com/kb/articles/flash-programming)

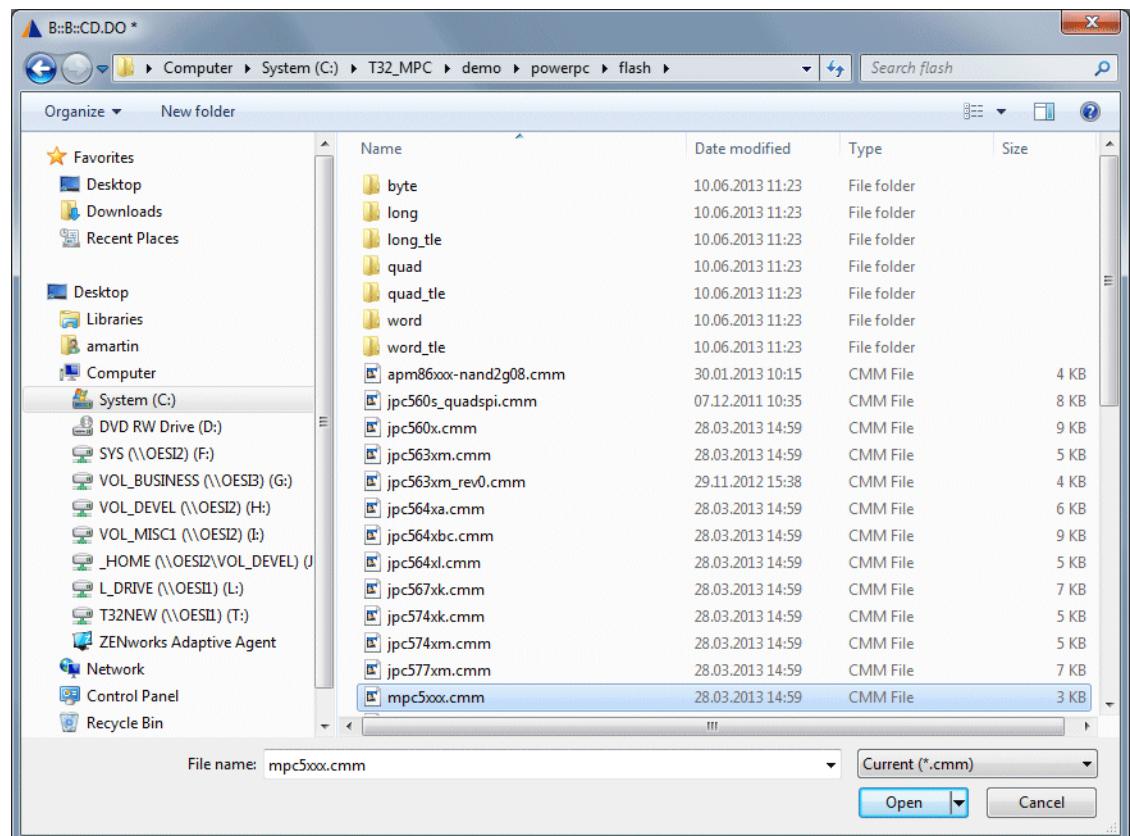

Ready-to-run scripts for most on-chip flashes can be found in `~/demo/<architecture>/flash/<cpu>.cmm`

e.g. `~/demo/arm/flash/mk20.cmm`

e.g. `~/demo/powerpc/flash/mpc5xxx.cmm`

To program the software to the on-chip flash of your processor/chip proceed as follows:

1. Start the script appropriate for your processor/chip.

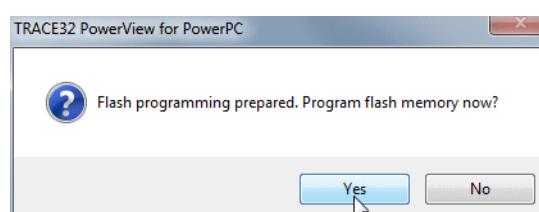

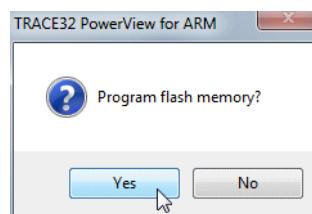

2. TRACE32 PowerView informs you when all preparations are done. Please confirm that you are ready to choose the boot loader or the application to be programmed.

3. Please select the boot loader or application to be programmed.

TRACE32 PowerView informs you, that the programming is done.

If the boot loader/application is compiled with debug symbols they are automatically loaded into TRACE32 PowerView with the flash programming.

For details on the on-chip flash programming open the flash programming script.

```

; ~~ represents the TRACE32 installation directory

PEDIT ~~/demo/powerpc/flash/mpc5xxxx.cmm

```

If you create your own start-up script for your target hardware, please call the flash programming script from there.

If you leave the flash programming script unchanged, you can always replace it with its most current version.

The following parameters can be used, when the flash programming script is called:

|                        |                                                                                                                                                                                                                                                      |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>CPU=&lt;cpu&gt;</b> | If a FLASH programming script supports a CPU family, you can provide your target CPU as parameter.                                                                                                                                                   |

| <b>PREPAREONLY</b>     | Advise the FLASH programming script to prepare the FLASH programming by declaring the FLASH sectors and by linking the appropriate programming binary. The FLASH programming commands are bypassed.                                                  |

| <b>DUALPORT=0 1</b>    | Disable/enable DualPort FLASH programming.<br>For all processors/cores that allow to <b>write to physical memory while the CPU is running</b> a higher FLASH programming performance can be achieved by the use of <b>DualPort FLASH Programming</b> |

Not every script supports all parameters. The parameters relevant for your script are described in the meta data section of the script.

```

; -----

; @Title: Generic script for Freescale MK20, MK21 and MK22 internal flash

;

; @Description:

;

; Example for flash declaration of Freescale MK20, MK21 and MK22 internal

; flash.

; Script arguments:

;

; DO mk20 [PREPAREONLY] [CPU=<cpu>] [DUALPORT=0|1] [MASSEREASE]

;

; PREPAREONLY only declares flash but does not execute flash programming

;

; CPU=<cpu> selects CPU derivative <cpu>. <cpu> can be CPU name out of the

; table listed below. For these derivatives the flash declaration

; is done by the script.

;

; DUALPORT default value is 0 (disabled). If DualPort mode is enabled

; flash algorithm stays running until flash programming is

; finished. Data is transferred via dual port memory access.

;

; MASSEREASE forces mass erase of device before establishing debug connection

;

; For example:

;

; DO --/demo/arm/flash/mk20 CPU=MK20DN512VLK10 DUALPORT=1 PREPAREONLY

; List of MK20/MK21/MK22 derivatives and their configuration:

;

; CPU-Type      Flash    ProgFlash   FlexNVM    EEPROM    RamSize

;   type        [Byte]   [Byte]      [Byte]     [Byte]    [Byte]

; -----

; MK20DN32VEX5    0      32KB       -         -       8KB

; MK20DN32VFM5    0      32KB       -         -       8KB

; MK20DN32VFT5    0      32KB       -         -       8KB

```

The following framework can be used to call the flash programming script from your start-up script.

```

...

DO <flash_script> [CPU=<cpu>] PREPAREONLY [DUALPORT=0|1]

; program file to on-chip FLASH

FLASH.ReProgram ALL /Erase

Data.LOAD.Elf <file>

FLASH.ReProgram off

; reset processor/chip

; might be necessary to reset all target settings made by the flash

; programming script

SYStem.Up

; continue with start-up script

;...

```

More details on the on-chip flash programming can be found in [“Onchip/NOR FLASH Programming User’s Guide”](#) (norflash.pdf).

TRACE32 PowerView provides two methods to program off-chip NOR flash:

## 1. Tool-based programming

Tool-based programming means that the flash programming algorithm is part of the TRACE32 software. Tool-based programming is easy to configure but slow.

## 2. Target-controlled programming

Target-controlled flash programming means that the underlying flash programming algorithm is detached from the TRACE32 software. Target-controlled flash programming works as follows:

1. The flash algorithm is downloaded to the target RAM.

2. The programming data are downloaded to the target RAM.

3. The flash algorithm running in the target RAM programs the data to the flash devices.

Target-controlled flash programming minimizes the communication between the host and the debugger hardware. This makes target-controlled flash programming fast.

**NOTE:**

It is recommended to start with tool-based flash programming. If this works properly you can switch to target-controlled flash programming.

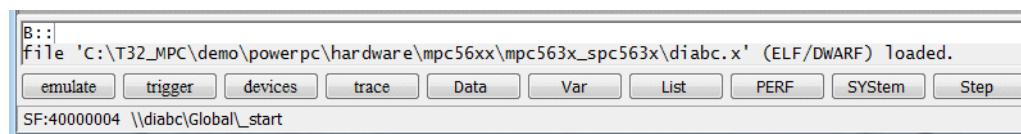

**Programming off-chip NOR flash requires the following steps (see next page):**

## 1. Disable Internal and External Watchdog

### Example

```

; Display "Watchdog Timer" configuration registers, highlight changes

PER.view , "Watchdog Timer" /SpotLight

```

```

; Disable Watchdog timer by configuring Watchdog Timer Control Register

; (WTCON)

PER.Set.simple 0x53000000 %Long 0x0

```

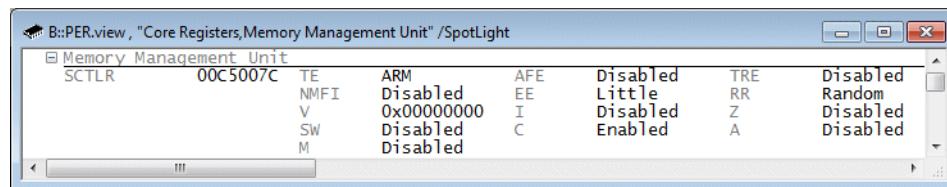

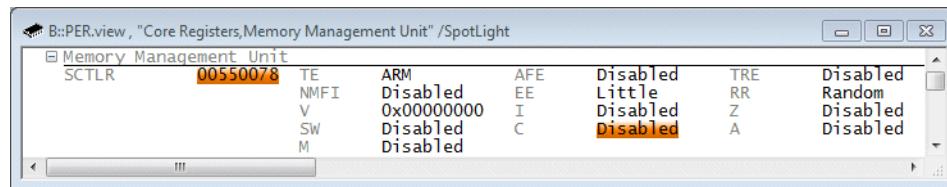

## 2. Disable Data Cache

The data cache has to be disabled for the address ranges of all flash devices to enable TRACE32 PowerView to read the flash status information.

### Example

```

; Display the memory management configuration registers

; highlight changes

PER.view , "Core Registers,Memory Management Unit" /SpotLight

```

```

; Disable Data Cache by configuring the control register SCLTR

PER.Set.simple C15:0x1 %Long 0x550078

```

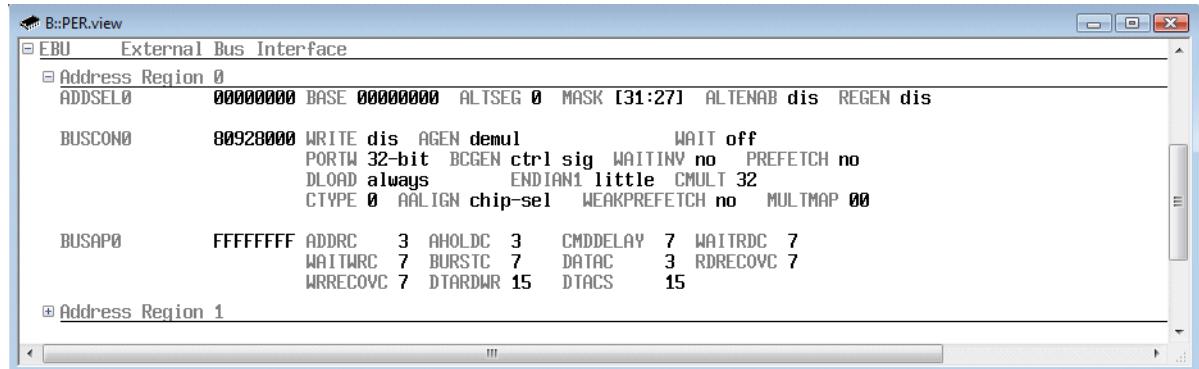

### 3. Make sure that the core has write access to the flash

NOR flash programming requires that the core has write access to the flash device(s).

The following settings in the **bus configuration** have to be done for each NOR flash device:

- Definition of the base address of the NOR flash device

- Definition of the size of the NOR flash device

- Definition of the bus size that is used to access the NOR flash device

- The write access has to be enabled for the NOR flash device

- Definition of the timing (number of wait states for the write access to the NOR flash device)

Use the **PER.view** command to check the settings in the bus configuration registers.

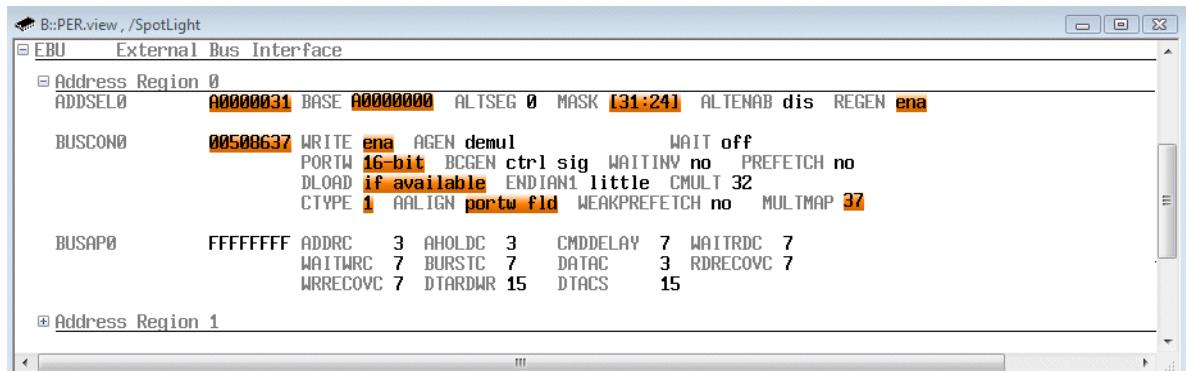

## Example for ColdFire

Bus configuration after reset:

In order to have write access to the used off-chip NOR flash device the **Address Region 0** has to be configured for the following characteristics:

- Base address 0xa0000000

- Size 16 MByte

- Bus size 16 bit

**PER.Set <address> %<format> <value>**

**Data.Set <address> %<format> <value>**

```

PER.view , /SpotLight ; Highlight all changed

; configuration registers

PER.Set 0xf0000080 %Long 0xA0000031 ; ADDSEL0

PER.Set 0xf00000c0 %Long 0x00508637 ; BUSCON0

```

Correct bus configuration for NOR flash programming.

|                                                                     |                                                                                                                                                                                                                                                                                                                                                                              |

|---------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>FLASH.RESet</b>                                                  | Reset the FLASH declaration table                                                                                                                                                                                                                                                                                                                                            |

| <b>FLASH.CFI</b> < <i>start_address</i> > < <i>data_bus_width</i> > | Generate a FLASH declaration by evaluating the Common Flash Interface description inside the FLASH device.<br>The command <b>FLASH.CFI</b> requires the definition of <ul style="list-style-type: none"><li>• the &lt;<i>start_address</i>&gt; of the FLASH device</li><li>• the &lt;<i>data_bus_width</i>&gt; that is used by the core to access the FLASH device</li></ul> |

| <b>FLASH.List</b>                                                   | List the FLASH declaration table                                                                                                                                                                                                                                                                                                                                             |

| <b>FLASH.UNLOCK ALL</b>                                             | Unlock the FLASH sectors                                                                                                                                                                                                                                                                                                                                                     |

| <b>FLASH.ReProgram ALL   OFF</b>                                    | Enable/disable the FLASH programming                                                                                                                                                                                                                                                                                                                                         |

| <b>Data.LOAD.&lt;sub_cmd&gt; &lt;file&gt; /&lt;option&gt;</b>       | Load code and debug symbols                                                                                                                                                                                                                                                                                                                                                  |

More details on the concepts of the TRACE32 NOR flash programming can be found in “[Onchip/NOR FLASH Programming User’s Guide](#)” (norflash.pdf).

If your FLASH device doesn’t provide CFI please refer to “[Onchip/NOR FLASH Programming User’s Guide](#)” (norflash.pdf) for details on the FLASH programming procedure.

## Example

```

FLASH.RESet ; Reset the FLASH declaration table

FLASH.CFI 0xa0000000 Word ; Generate a FLASH declaration via

; CFI

FLASH.List ; Display the FLASH declaration

; table

FLASH.UNLOCK ALL ; Unlock the FLASH device if

; required

; e.g. some FLASH devices are

; locked after power on

FLASH.ReProgram ALL ; Enable the FLASH for programming

Data.LOAD.Elf demo.elf ; Specify the file that contains

; the code and the debug symbols

FLASH.ReProgram off ; Program FLASH and disable

; the FLASH programming afterwards

Data.LOAD.Elf demo.elf /DIFF ; Verify the FLASH programming

IF FOUND()

PRINT "Verify error after FLASH programming"

ELSE

PRINT "FLASH programming completed successfully"

```

**FLASH.RESet**

Reset the FLASH declaration table

**FLASH.CFI** <*start\_address*> <*bus\_width*> /**TARGET** <*code\_range*> <*data\_range*>

Generate a FLASH declaration by evaluating the Common Flash Interface description inside the FLASH device.

The command **FLASH.CFI** requires the definition of

- the <*start\_address*> of the FLASH device

- the <*data\_bus\_width*> that is used by the core to access the FLASH device

- the target RAM location <*code\_range*> for the flash programming algorithm

- the target RAM location <*data\_range*> for the flash programming data

**FLASH.List**

List the FLASH declaration table

**FLASH.UNLOCK ALL**

Unlock the FLASH sectors

**FLASH.ReProgram ALL | OFF**

Enable/disable the FLASH programming

**Data.LOAD.<sub\_cmd> <file> /<option>**

Load code and debug symbols

## Details on `<code_range>`

Required size for the code is `size_of(file) + 32 byte`

|                             |                                                        |

|-----------------------------|--------------------------------------------------------|

| Flash programming algorithm | Memory mapping for the <code>&lt;code_range&gt;</code> |

| 32 byte                     |                                                        |

## Details on `<data_range>`

The parameter `<data_range>` specifies the RAM location for the data, especially

- the `<data_buffer_size>` for the programming data. Recommended buffer size is 4 KByte, smaller buffer sizes are also possible. The max. buffer size is 16 KByte

- the argument buffer for the communication between TRACE32 PowerView and the programming algorithm

- the stack

```

<data_buffer_size> =

size_of(<data_range>) - 64 byte argument buffer - 256 byte stack

```

|                                                                                                                                                          |                                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

| 64 byte argument buffer                                                                                                                                  | Memory mapping for the <code>&lt;data_range&gt;</code> |

| Data buffer for data transfer<br>between TRACE32 and<br>flash programming algorithm<br><code>&lt;buffer_size&gt;</code> calculated as<br>described above |                                                        |

| 256 byte stack                                                                                                                                           |                                                        |

#### 4. Enable RAM Access

Target-controlled Flash Programming requires, that the core has access to the RAM locations specified for *<code\_range>* and *<data\_range>*.

If this is not the case the following settings in the **bus configuration** have to be done for an off-chip RAM:

- Definition of the base address of the RAM

- Definition of the size of the RAM

- Definition of the bus size that is used to access the RAM

- Definition of the timing (number of wait states for the RAM access)

## Example

```

; reset the FLASH declaration table

FLASH.RESet

; set up the FLASH declaration for target-controlled programming

; target RAM at address 0x20000000

FLASH.CFI 0x0 Word /TARGET 0x20000000++0xffff 0x20001000++0xffff

; display FLASH declaration table

FLASH.List

; unlock the FLASH device if required for a power-up locked device

; FLASH.UNLOCK ALL

; enable the programming for all declared FLASH devices

FLASH.ReProgram ALL

; specify the file that contains the code and the debug symbols

Data.LOAD.Elf demo.elf

; program the file and disable the FLASH programming afterwards

FLASH.ReProgram off

; verify the FLASH contents

Data.LOAD.Elf demo.elf /DIFF

IF FOUND()

PRINT "Verify error after FLASH programming"

ELSE

PRINT "FLASH programming completed successfully"

...

```

## Configure the TRACE32 OS Awareness

---

Refer to “[The \*\*TASK.CONFIG\*\* Command](#)”, page 8 for details.

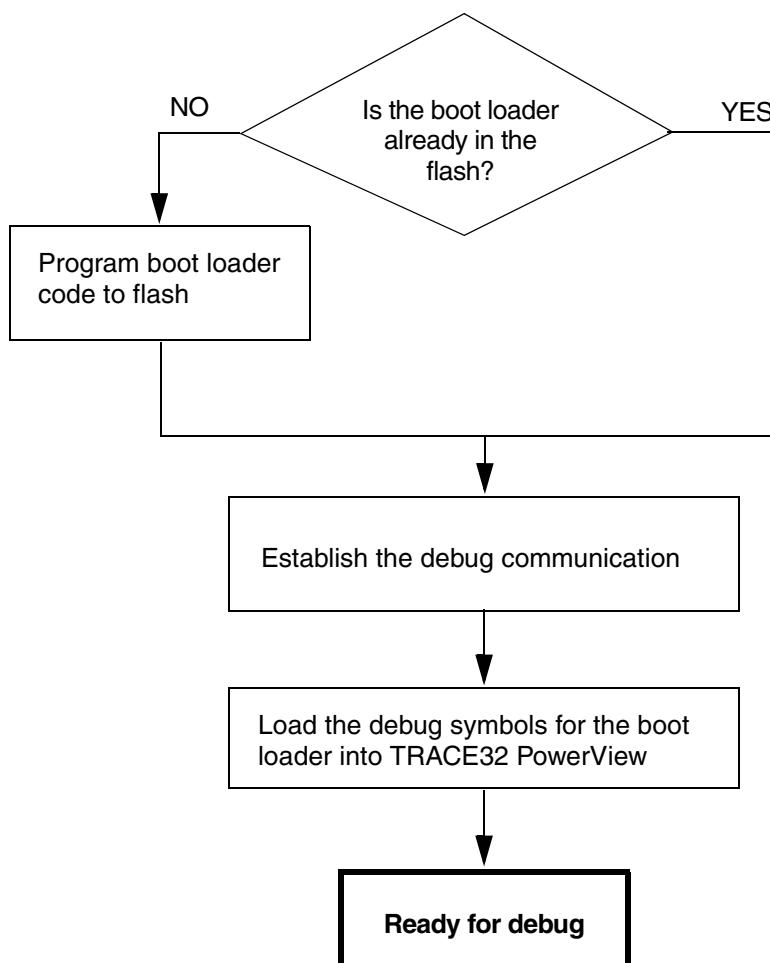

# Debug Scenario 2

---

The boot loader under debug is running out of a flash e.g. a NAND flash.

In contrast to NOR flash, code can not be executed out of NAND or serial flash. The code has always to be copied to RAM before it can be executed.

## Typical Boot Sequence

---

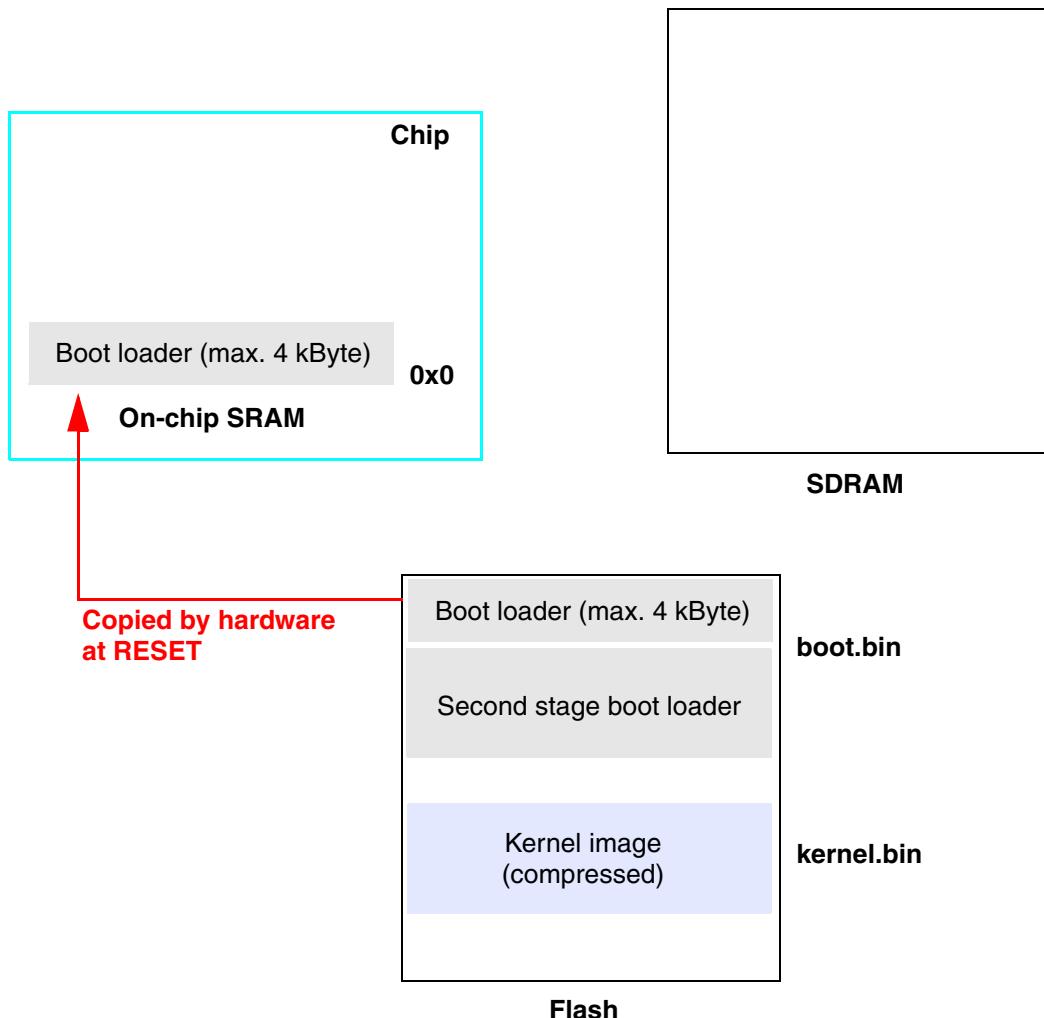

Before the setup for debug scenario 2 is described, it might be useful to have a look at a typical boot sequence. If the boot loader is running out of flash the system start-up might include the following steps:

## 1. Reset

At RESET the boot loader is copied from the flash to an on-chip SRAM, which is mapped to the reset vector. The boot loader starts afterwards.

Please be aware, that some core(s) require a correct ECC for this copy procedure.

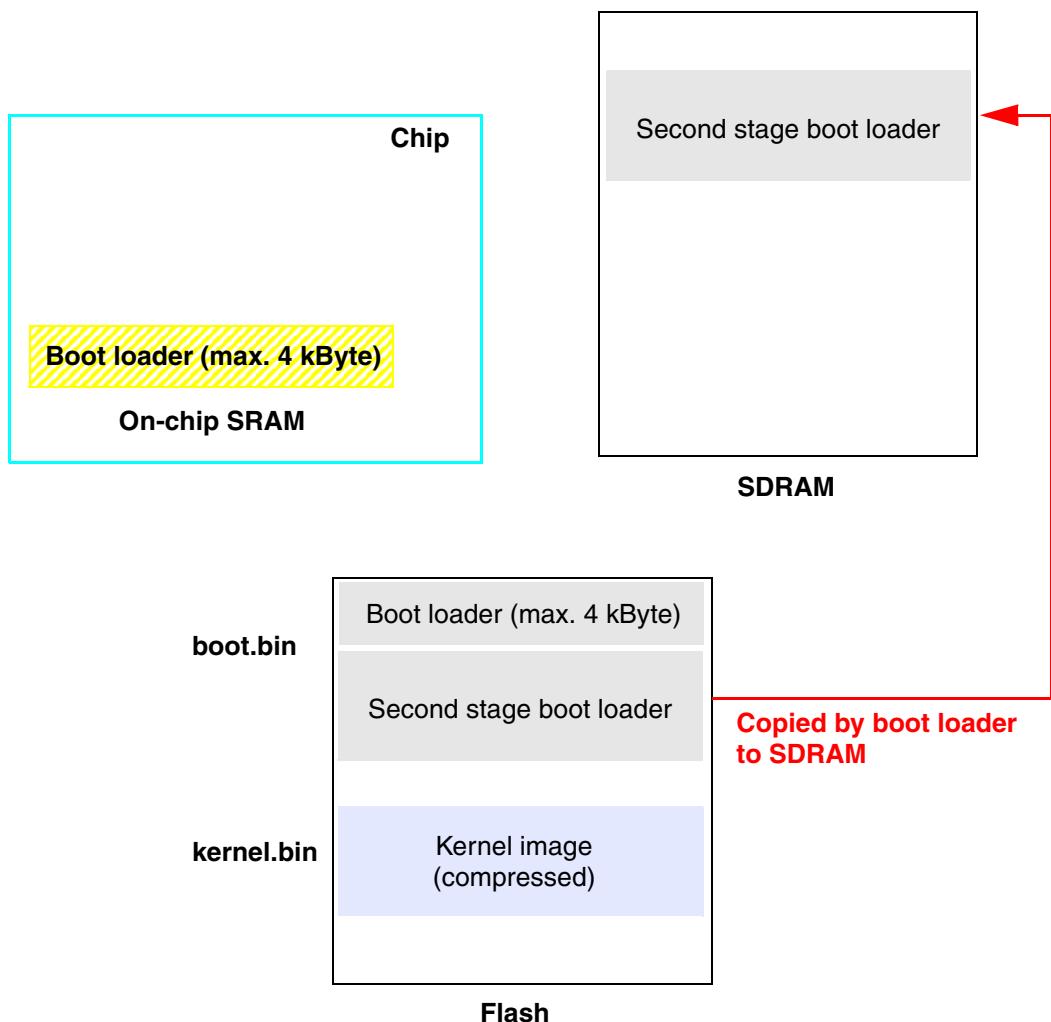

## 2. Boot loader is running

The main task of the boot loader is to initialize the SDRAM and to copy the second stage boot loader to SDRAM. When this is done the control is passed to the second stage boot loader.

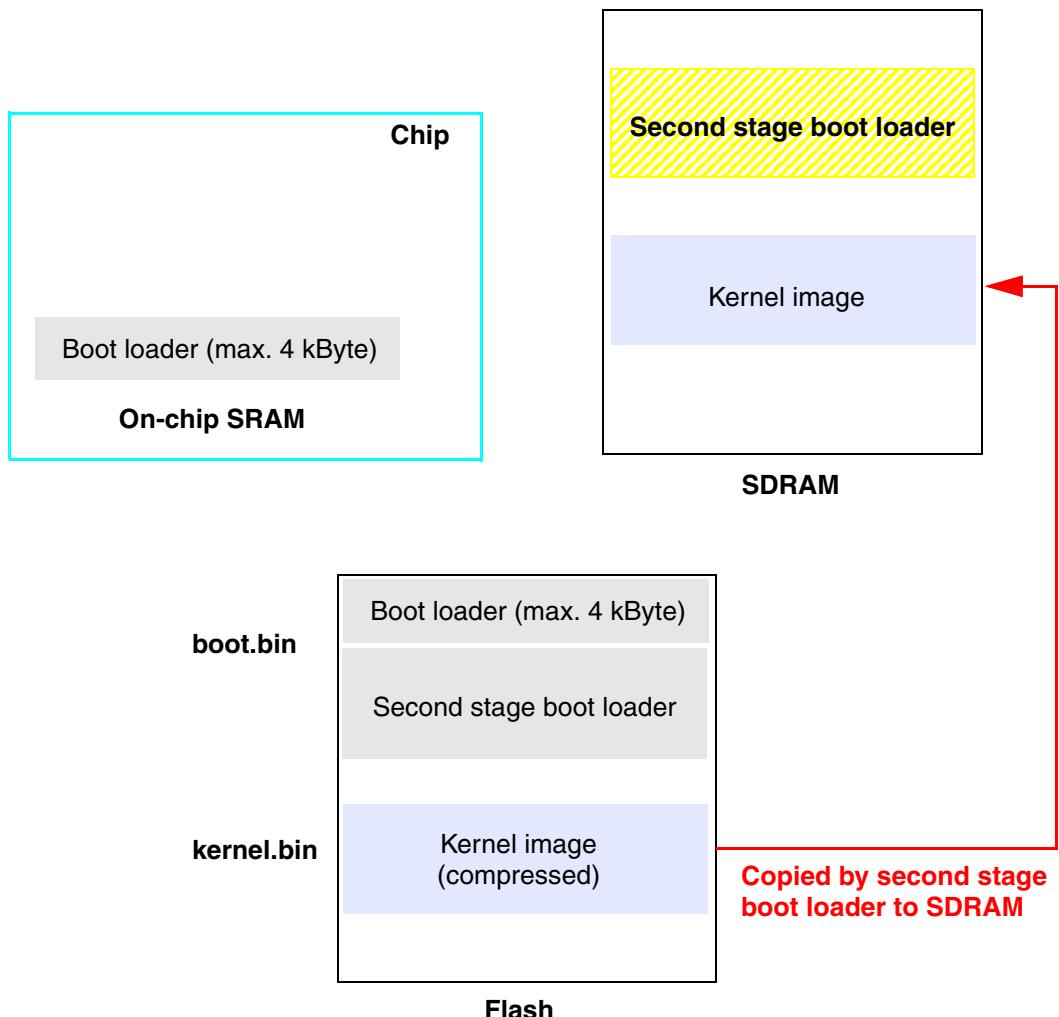

### 3. Second stage boot loader is running

The main task of the second stage boot loader is to copy the kernel image to SDRAM. When this is done the control is passed to the kernel.

**NOTE:** Flash programming requires that data cache and MMU are disabled.

## The Flash Programming File and the Debug Symbol File

---

Flash programming can only program binary files. Therefore two output files have to be generated by the compiler:

- A binary file (e.g. boot.bin)

- A file containing the debug symbols (e.g. boot.elf)

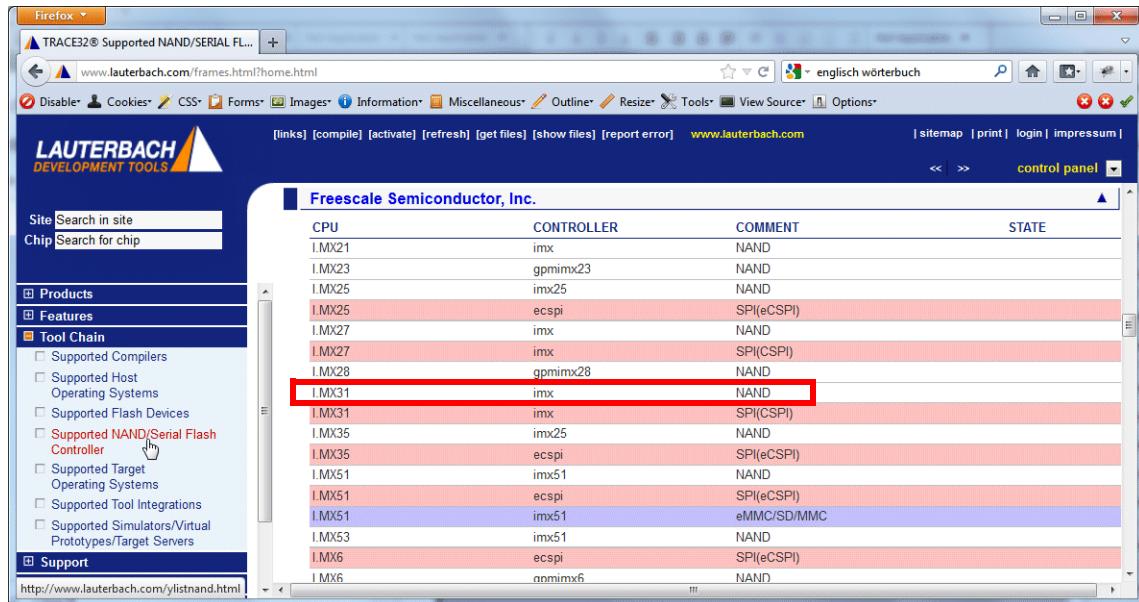

# NAND Flash Programming (non-generic NAND Flash Controller)

Ready-to-run flash programming scripts for most processors/chips can be found in the directory

~~/demo/<architecture>/flash

Folder and file name convention:

~~/demo/<architecture>/flash/<cpu\_name>-<prefix\_of\_nand\_flash\_code>.cmm

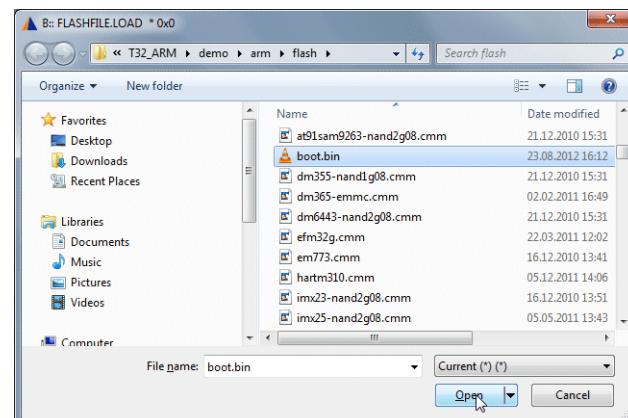

Get <cpu\_name> from the CPU column of the list of “**Supported NAND/Serial Flash Controller**” on the Lauterbach home page ([www.lauterbach.com](http://www.lauterbach.com)) if the CONTROLLER column does not indicate generic.

| CPU   | CONTROLLER | COMMENT     | STATE |

|-------|------------|-------------|-------|

| IMX21 | imx        | NAND        |       |

| IMX23 | gpmimx23   | NAND        |       |

| IMX25 | imx25      | NAND        |       |

| IMX25 | ecspi      | SPI(eCSPI)  |       |

| IMX27 | imx        | NAND        |       |

| IMX27 | imx        | SPI(CSPI)   |       |

| IMX28 | gpmimx28   | NAND        |       |

| IMX31 | imx        | NAND        |       |

| IMX31 | imx        | SPI(CSPI)   |       |

| IMX35 | imx25      | NAND        |       |

| IMX35 | ecspi      | SPI(eCSPI)  |       |

| IMX51 | imx51      | NAND        |       |

| IMX51 | ecspi      | SPI(eCSPI)  |       |

| IMX51 | imx51      | eMMC/SD/MMC |       |

| IMX53 | imx51      | NAND        |       |

| IMX6  | ecspi      | SPI(eCSPI)  |       |

| IMX6  | nnmimx6    | NAND        |       |

If the **CONTROLLER** column indicates **generic** refer to “[NAND Flash Programming \(generic NAND Flash Controller\)](#)”, page 45.

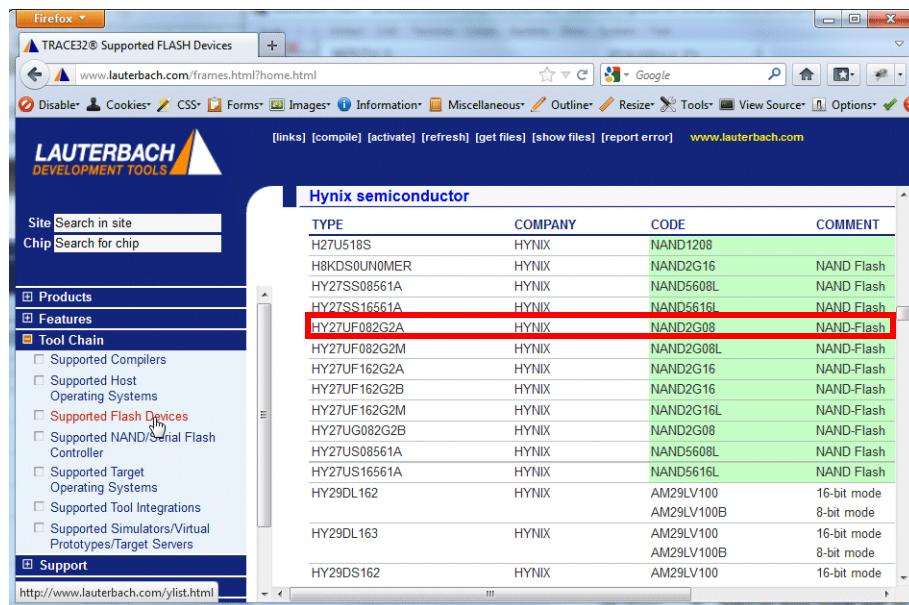

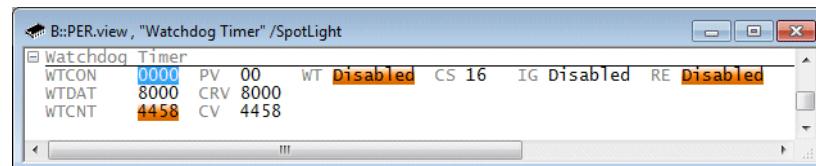

Get the prefix of the <nand\_flash\_code> from the CODE column of the list of “**Supported Flash Devices**” on the Lauterbach home page ([www.lauterbach.com](http://www.lauterbach.com)).

The screenshot shows a Firefox browser window with the Lauterbach website open. The URL is [www.lauterbach.com/frames.html?home.html](http://www.lauterbach.com/frames.html?home.html). The page title is "TRACE32® Supported FLASH Devices". On the left, a sidebar menu is open under "Tool Chain", with "Supported Flash Devices" selected. The main content area is titled "Hynix semiconductor" and contains a table with the following data:

| TYPE                | COMPANY      | CODE            | COMMENT           |

|---------------------|--------------|-----------------|-------------------|

| H27U518S            | HYNIX        | NAND1208        |                   |

| H8KDSOUN0MER        | HYNIX        | NAND2G16        | NAND Flash        |

| HY27SS08561A        | HYNIX        | NAND5608L       | NAND Flash        |

| HY27SS16561A        | HYNIX        | NAND5616L       | NAND Flash        |

| <b>HY27UF082G2A</b> | <b>HYNIX</b> | <b>NAND2G08</b> | <b>NAND-Flash</b> |

| HY27UF082G2M        | HYNIX        | NAND2G08L       | NAND-Flash        |

| HY27UF162G2A        | HYNIX        | NAND2G16        | NAND-Flash        |

| HY27UF162G2B        | HYNIX        | NAND2G16        | NAND-Flash        |

| HY27UF162G2M        | HYNIX        | NAND2G16L       | NAND-Flash        |

| HY27UG082G2B        | HYNIX        | NAND2G08        | NAND-Flash        |

| HY27US08561A        | HYNIX        | NAND5608L       | NAND Flash        |

| HY27US16561A        | HYNIX        | NAND5616L       | NAND Flash        |

| HY29DL162           | HYNIX        | AM29LV100       | 16-bit mode       |

|                     |              | AM29LV100B      | 8-bit mode        |

| HY29DL163           | HYNIX        | AM29LV100       | 16-bit mode       |

|                     |              | AM29LV100B      | 8-bit mode        |

| HY29DS162           | HYNIX        | AM29LV100       | 16-bit mode       |

Name of flash programming script here `~/demo/arm/flash/imx31-nand2g08.cmm`

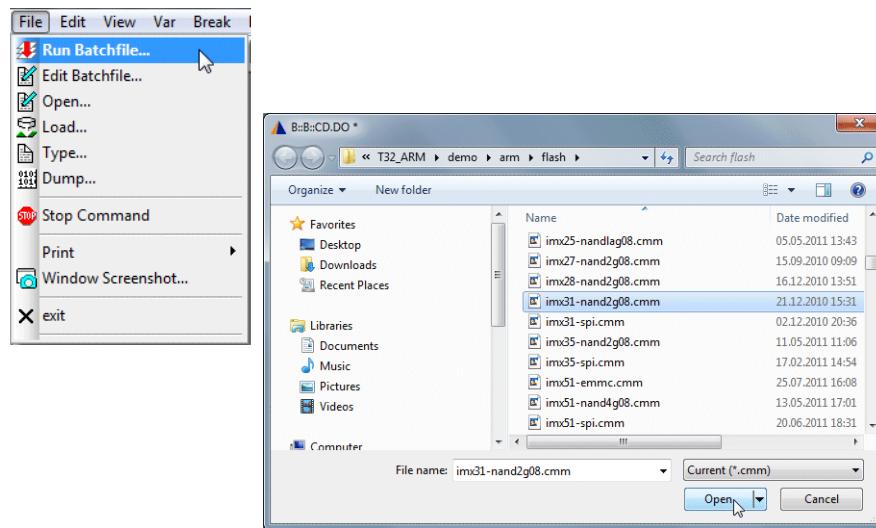

To program the code to flash proceed as follows:

1. Start the script appropriate for your processor/chip and appropriate for your flash device.

2. TRACE32 PowerView informs you when all preparations are done. Please confirm that you are ready to choose the boot loader binary to be programmed.

3. Please select the boot loader to be programmed.

Detail on NAND flash programming can be found in [“NAND FLASH Programming User’s Guide”](#) (handflash.pdf).

# NAND Flash Programming (generic NAND Flash Controller)

The **CONTROLLER** column of the list of “**Supported NAND/Serial Flash Controller**” on the Lauterbach home page ([www.lauterbach.com](http://www.lauterbach.com)) indicates “generic”, if a processor/chip has a generic NAND flash controller.

| CPU                          | CONTROLLER | COMMENT     | STATE |

|------------------------------|------------|-------------|-------|

| SH7264                       | sh7264     | NAND        |       |

| SH7264                       | sh7264     | SPI         |       |

| <b>Samsung Semiconductor</b> |            |             |       |

| S3C24XX                      | generic    | NAND        |       |

| S3C6410                      | s3c6410    | OneNAND     |       |

| S3C6410                      | s3c6410    | eMMC/SD/MMC |       |

| S3C64XX                      | generic    | NAND        |       |

Programming script for generic NAND flash controller have to be written by the user.

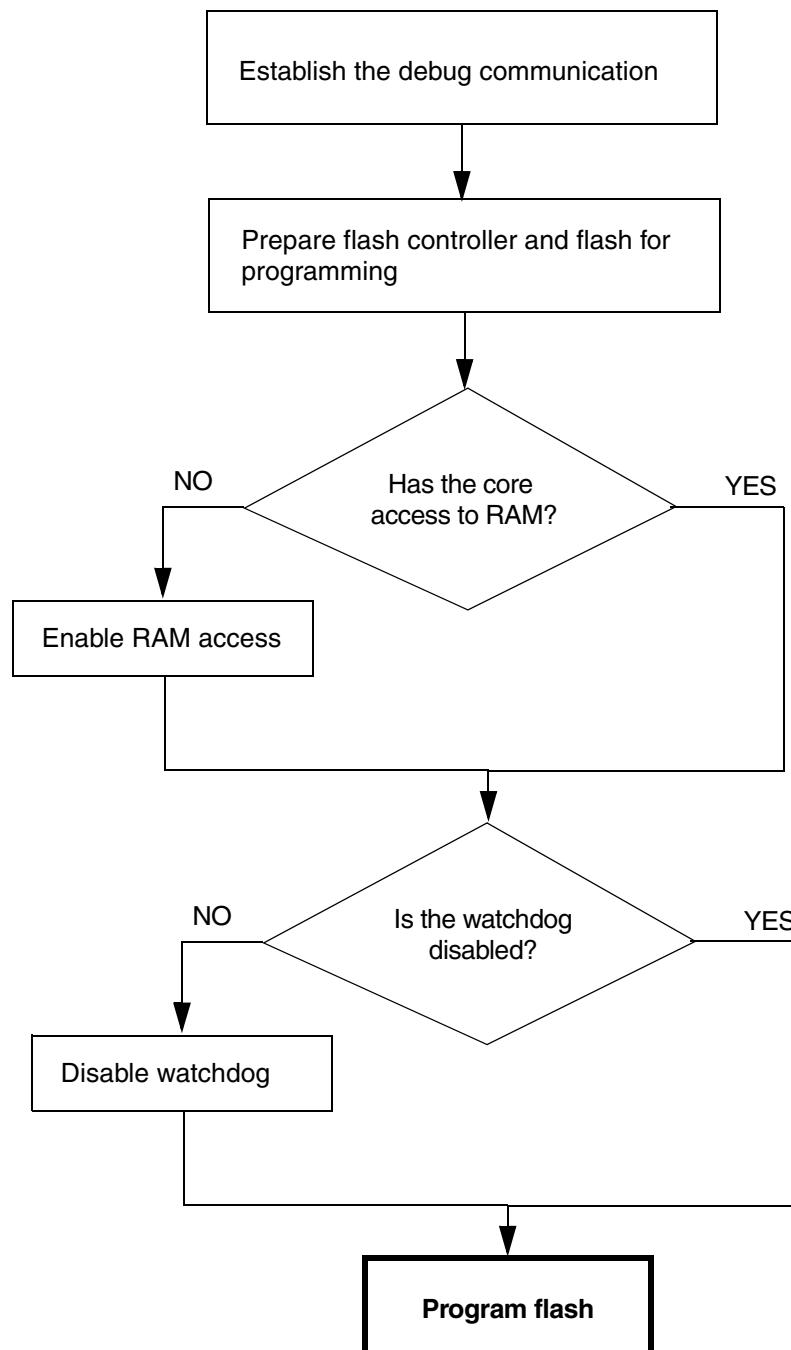

## 1. Prepare the NAND FLASH Controller and the NAND FLASH for Programming

Programming a flash device requires a proper initialization of the flash controller and the bus interface. The following settings might be necessary:

- Power up the flash clock domain.

- Enable the flash controller or bus.

- Configure the communication signals (clock, timing, etc.).

- Inform the flash controller about the flash device (large/small page, ECC, spare, etc.).

- Configure the flash pins if they are muxed with other functions of the processor/chip.

- Disable the write protection for the flash.

Use the **PER.Set/PER.view** commands for this setup.

Example for s3c2410X (ARM920T):

```

PER.view , "NAND Flash Controller" /SpotLight

```

| B:PER.view , "NAND Flash Controller" /SpotLight |          |         |          |         |                 |         |          |         |

|-------------------------------------------------|----------|---------|----------|---------|-----------------|---------|----------|---------|

| NAND Flash Controller                           |          |         |          |         |                 |         |          |         |

| NFCONF                                          | 00004800 | ENABLE  | Disabled | INI_ECC | Not initialized | NFM_CEN | Inactive | TACLS 0 |

|                                                 |          |         |          | TWRPH0  | 0               |         |          |         |

| NFCMD                                           | 00000000 | COMMAND | 00       |         |                 |         |          |         |

| NFADDR                                          | 00000000 | ADDRESS | 00       |         |                 |         |          |         |

| NFDATA                                          | 00000000 | DATA    | 00       |         |                 |         |          |         |

| NFSTAT                                          | 00008301 | RNB     | Ready    |         |                 |         |          |         |

| NFECC                                           | 00559595 | ECC2    | 55       | ECC1    | 95              | ECC0    | 95       |         |

```

; enable and configure NAND flash controller

PER.Set 0x4E000000 %Long 0xE030

```

| B:PER.view , "NAND Flash Controller" /SpotLight |          |         |         |         |                 |         |        |         |

|-------------------------------------------------|----------|---------|---------|---------|-----------------|---------|--------|---------|

| NAND Flash Controller                           |          |         |         |         |                 |         |        |         |

| NFCONF                                          | 0000E030 | ENABLE  | Enabled | INI_ECC | Not initialized | NFM_CEN | Active | TACLS 0 |

|                                                 |          |         |         | TWRPH0  | 3               |         |        |         |

| NFCMD                                           | 00000000 | COMMAND | 00      |         |                 |         |        |         |

| NFADDR                                          | 00000000 | ADDRESS | 00      |         |                 |         |        |         |

| NFDATA                                          | 00000004 | DATA    | 04      |         |                 |         |        |         |

| NFSTAT                                          | 00008301 | RNB     | Ready   |         |                 |         |        |         |

| NFECC                                           | 00C0C00C | ECC2    | C0      | ECC1    | C0              | ECC0    | 0C     |         |

## 2. Enable RAM Access

TRACE32 PowerView runs the flash programming algorithm in target RAM. It requires at least 16 KByte of RAM for this purpose.

This requires that the core has access to target RAM.

If the core has no access to target RAM, the access to target RAM has to be set up.

Correct settings in the bus configuration registers are key for the RAM access. The following settings in the bus configuration have to be done:

- Definition of the RAM base address

- Definition of the RAM size

- Definition of the bus size that is used to access the RAM

- The write access has to be enabled for the RAM

- Definition of the timing (number of wait states for the write access to the RAM)

Use the **PER.Set/PER.view** commands for this setup.

## Example SDRAM configuration on an s3c2410X (ARM920T):

Bus configuration after reset:

| B:PER.view, /SpotLight                      |             |            |          |           |           |         |          |

|---------------------------------------------|-------------|------------|----------|-----------|-----------|---------|----------|

| ARM Core Registers                          |             |            |          |           |           |         |          |

| Memory Controller                           |             |            |          |           |           |         |          |

| BWSCON 00000000                             |             |            |          |           |           |         |          |

| ST7                                         | No UB/LB    | WS7        | Disabled | DW7       | 8-bit     |         |          |

| ST6                                         | No UB/LB    | WS6        | Disabled | DW6       | 8-bit     |         |          |

| ST5                                         | No UB/LB    | WS5        | Disabled | DW5       | 8-bit     |         |          |

| ST4                                         | No UB/LB    | WS4        | Disabled | DW4       | 8-bit     |         |          |

| ST3                                         | No UB/LB    | WS3        | Disabled | DW3       | 8-bit     |         |          |

| ST2                                         | No UB/LB    | WS2        | Disabled | DW2       | 8-bit     |         |          |

| ST1                                         | No UB/LB    | WS1        | Disabled | DW1       | 8-bit     |         |          |

| DW0                                         | Reserved    |            |          |           |           |         |          |

| BANK CONTROL REGISTER(BANKCONN:nGCS0-nGCS5) |             |            |          |           |           |         |          |

| BANKCON0 00000700                           |             |            |          |           |           |         |          |

| TACS                                        | 0 clock     | TCOS       | 0 clock  | TACC      | 14 clocks |         |          |

| TCOH                                        | 1 clock     | TCAH       | 0 clock  | TACP      | 2 clocks  |         |          |

| PMC                                         | 1 data      |            |          |           |           |         |          |

| BANKCON1 00000700                           |             |            |          |           |           |         |          |

| TACS                                        | 0 clock     | TCOS       | 0 clock  | TACC      | 14 clocks |         |          |

| TCOH                                        | 0 clock     | TCAH       | 0 clock  | TACP      | 2 clocks  |         |          |

| PMC                                         | 1 data      |            |          |           |           |         |          |

| BANKCON2 00000700                           |             |            |          |           |           |         |          |

| TACS                                        | 0 clock     | TCOS       | 0 clock  | TACC      | 14 clocks |         |          |

| TCOH                                        | 0 clock     | TCAH       | 0 clock  | TACP      | 2 clocks  |         |          |

| PMC                                         | 1 data      |            |          |           |           |         |          |

| BANKCON3 00000700                           |             |            |          |           |           |         |          |

| TACS                                        | 0 clock     | TCOS       | 0 clock  | TACC      | 14 clocks |         |          |

| TCOH                                        | 0 clock     | TCAH       | 0 clock  | TACP      | 2 clocks  |         |          |

| PMC                                         | 1 data      |            |          |           |           |         |          |

| BANKCON4 00000700                           |             |            |          |           |           |         |          |

| TACS                                        | 0 clock     | TCOS       | 0 clock  | TACC      | 14 clocks |         |          |

| TCOH                                        | 0 clock     | TCAH       | 0 clock  | TACP      | 2 clocks  |         |          |

| PMC                                         | 1 data      |            |          |           |           |         |          |

| BANKCON5 00000700                           |             |            |          |           |           |         |          |

| TACS                                        | 0 clock     | TCOS       | 0 clock  | TACC      | 14 clocks |         |          |

| TCOH                                        | 0 clock     | TCAH       | 0 clock  | TACP      | 2 clocks  |         |          |

| PMC                                         | 1 data      |            |          |           |           |         |          |

| BANKCON6 00018008                           |             |            |          |           |           |         |          |

| MT                                          | Sync DRAM   | TRCD       | 4 clocks | SCAN      | 8-bit     |         |          |

| BANKCON7 00018008                           |             |            |          |           |           |         |          |

| MT                                          | Sync DRAM   | TRCD       | 4 clocks | SCAN      | 8-bit     |         |          |

| REFRESH CONTROL REGISTER                    |             |            |          |           |           |         |          |

| REFRESH 00AC0000                            | REFEN       | Enabled    | TREFMD   | Auto      |           | TRP     | 4 clocks |

| TSRC                                        | 7 clocks    |            | REFCNT   | 0000      |           |         |          |

| BANKSIZE REGISTER                           |             |            |          |           |           |         |          |

| BANKSIZE 00000002                           | BURST_EN    | Disabled   | SCKE_EN  | Disabled  |           | SCLK_EN | Disabled |

| BK76MAP                                     | 128MB/128MB |            |          |           |           |         |          |

| SDRAM MODE REGISTER SET REGISTER            |             |            |          |           |           |         |          |

| MRSRB6 00000030                             | WBL         | Burst      | TM       | Test mode |           | CL      | 3 clocks |

|                                             | BT          | Sequential | BL       | 1         |           |         |          |

| MRSRB7 00000030                             | WBL         | Burst      | TM       | Test mode |           | CL      | 3 clocks |

|                                             | BT          | Sequential | BL       | 1         |           |         |          |

```

PER.Set 0x48000000 %Long 0x2222D222

PER.Set 0x48000004 %Long 0x00000700

PER.Set 0x48000008 %Long 0x00007fff

PER.Set 0x4800000C %Long 0x00000700

PER.Set 0x48000010 %Long 0x00001F4C

PER.Set 0x48000014 %Long 0x00000700

PER.Set 0x48000018 %Long 0x00000700

PER.Set 0x4800001C %Long 0x00018005

PER.Set 0x48000020 %Long 0x00018005

PER.Set 0x48000024 %Long 0x008e0459

PER.Set 0x48000028 %Long 0x00000032

PER.Set 0x4800002C %Long 0x00000030

PER.Set 0x48000030 %Long 0x00000030

PER.Set 0x53000030 %Long 0x00000000

```

## Correct bus configuration for SDRAM usage:

| ARM Core Registers                                   |                 |          |                 |         |                 |         |                 |

|------------------------------------------------------|-----------------|----------|-----------------|---------|-----------------|---------|-----------------|

| <b>Memory Controller</b>                             |                 |          |                 |         |                 |         |                 |

| BWSCON                                               | <b>2222D220</b> | ST7      | No UB/LB        | WS7     | Disabled        | DW7     | 32-bit          |

|                                                      |                 | ST6      | No UB/LB        | WS6     | Disabled        | DW6     | 32-bit          |

|                                                      |                 | ST5      | No UB/LB        | WS5     | Disabled        | DW5     | 32-bit          |

|                                                      |                 | ST4      | No UB/LB        | WS4     | Disabled        | DW4     | 32-bit          |

|                                                      |                 | ST3      | UB/LB           | WS3     | <b>Enabled</b>  | DW3     | 16-bit          |

|                                                      |                 | ST2      | No UB/LB        | WS2     | Disabled        | DW2     | 32-bit          |

|                                                      |                 | ST1      | No UB/LB        | WS1     | Disabled        | DW1     | 32-bit          |

|                                                      |                 | DW0      | Reserved        |         |                 |         |                 |

| <b>BANK CONTROL REGISTER (BANKCONN: nGCS0-nGCS5)</b> |                 |          |                 |         |                 |         |                 |

| BANKCON0                                             | <b>00000700</b> | TACS     | 0 clock         | TCOS    | 0 clock         | TACC    | 14 clocks       |

|                                                      |                 | TCOH     | 0 clock         | TCAH    | 0 clock         | TACP    | 2 clocks        |

|                                                      |                 | PMC      | 1 data          |         |                 |         |                 |

| BANKCON1                                             | <b>00007FF0</b> | TACS     | <b>4 clocks</b> | TCOS    | <b>4 clocks</b> | TACC    | 14 clocks       |

|                                                      |                 | TCOH     | <b>4 clocks</b> | TCAH    | <b>4 clocks</b> | TACP    | 2 clocks        |

|                                                      |                 | PMC      | 1 data          |         |                 |         |                 |

| BANKCON2                                             | <b>00000700</b> | TACS     | 0 clock         | TCOS    | 0 clock         | TACC    | 14 clocks       |

|                                                      |                 | TCOH     | 0 clock         | TCAH    | 0 clock         | TACP    | 2 clocks        |

|                                                      |                 | PMC      | 1 data          |         |                 |         |                 |

| BANKCON3                                             | <b>00001F4C</b> | TACS     | 0 clock         | TCOS    | <b>4 clocks</b> | TACC    | 14 clocks       |

|                                                      |                 | TCOH     | <b>1 clock</b>  | TCAH    | 0 clock         | TACP    | <b>6 clocks</b> |

|                                                      |                 | PMC      |                 |         |                 |         |                 |

| BANKCON4                                             | <b>00000700</b> | TACS     | 0 clock         | TCOS    | 0 clock         | TACC    | 14 clocks       |

|                                                      |                 | TCOH     | 0 clock         | TCAH    | 0 clock         | TACP    | 2 clocks        |

|                                                      |                 | PMC      | 1 data          |         |                 |         |                 |

| BANKCON5                                             | <b>00000700</b> | TACS     | 0 clock         | TCOS    | 0 clock         | TACC    | 14 clocks       |

|                                                      |                 | TCOH     | 0 clock         | TCAH    | 0 clock         | TACP    | 2 clocks        |

|                                                      |                 | PMC      | 1 data          |         |                 |         |                 |

| BANKCON6                                             | <b>00018005</b> | MT       | Sync DRAM       | TRCD    | <b>3 clocks</b> | SCAN    | 8-bit           |

| BANKCON7                                             | <b>00018005</b> | MT       | Sync DRAM       | TRCD    | <b>3 clocks</b> | SCAN    | 8-bit           |

| <b>REFRESH CONTROL REGISTER</b>                      |                 |          |                 |         |                 |         |                 |

| REFRESH                                              | <b>008E0459</b> | REFEN    | Enabled         | TREFMD  | Auto            | TRP     | <b>2 clocks</b> |

|                                                      |                 | TSRC     | 7 clocks        | REFCNT  | 0459            |         |                 |

| <b>BANKSIZE REGISTER</b>                             |                 |          |                 |         |                 |         |                 |

| BANKSIZE                                             | <b>00000032</b> | BURST_EN | Disabled        | SCKE_EN | <b>Enabled</b>  | SCLK_EN | <b>Enabled</b>  |

|                                                      |                 | BK76MAP  | 128MB/128MB     |         |                 |         |                 |

| <b>SDRAM MODE REGISTER SET REGISTER</b>              |                 |          |                 |         |                 |         |                 |

| MRSRB6                                               | <b>00000030</b> | WBL      | Burst           | TM      | Test mode       | CL      | 3 clocks        |

|                                                      |                 | BT       | Sequential      | BL      | 1               |         |                 |

| MRSRB7                                               | <b>00000030</b> | WBL      | Burst           | TM      | Test mode       | CL      | 3 clocks        |

|                                                      |                 | BT       | Sequential      | BL      | 1               |         |                 |

### 3. Disable internal and external watchdog

Example (ARM920T):

```

; Display "Watchdog Timer" configuration registers, highlight changes

PER.view , "Watchdog Timer" /SpotLight

```

```

; Disable Watchdog timer by configuring Watchdog Timer Control Register

; (WTCN)

PER.Set.simple 0x53000000 %Long 0x0

```

The following commands are useful, if a generic NAND flash controller is used to program a flash. For details refer to “**NAND FLASH Programming User’s Guide**” (nandflash.pdf).

|                                                          |                                                                            |

|----------------------------------------------------------|----------------------------------------------------------------------------|

| <b>FLASHFILE.RESet</b>                                   | Reset NAND flash programming to default.                                   |

| <b>FLASHFILE.CONFIG</b> <cmd_reg> <addr_reg> <io_reg>    | Inform TRACE32 PowerView on the NAND flash registers                       |

| <b>FLASHFILE.TARGET</b> <code_range> <data_range> <file> | Inform TRACE32 PowerView on all details about flash programming algorithm. |

| <b>FLASHFILE.Erase</b> <range>                           | Erase NAND flash.                                                          |

| <b>FLASHFILE.LOAD</b> <file> <address>                   | Program binary file to NAND flash.                                         |

More details on the **FLASHFILE.TARGET** command:

The name of the flash programming algorithm depends on the NAND flash to be programmed (e.g. nand5608.bin for the K9F5608 NAND flash from Samsung).

| K8P6415        | SAMSUNG        | AM29LV100       |                      |

|----------------|----------------|-----------------|----------------------|

| K8Q2815        | SAMSUNG        | AM29LV100       |                      |

| K8S2815        | SAMSUNG        | AM29LV100       |                      |

| K8S3215        | SAMSUNG        | AM29LV100       |                      |

| K8S6115        | SAMSUNG        | AM29LV100       |                      |

| K8S6415        | SAMSUNG        | AM29LV100       |                      |

| K9F1208        | SAMSUNG        | NAND1208        | NAND Flash           |

| K9F1G08        | SAMSUNG        | NAND1G08        | NAND Flash           |

| K9F2G08        | SAMSUNG        | NAND2G08        | NAND Flash           |

| K9F4G08        | SAMSUNG        | NAND2G08        | NAND Flash           |

| <b>K9F5608</b> | <b>SAMSUNG</b> | <b>NAND5608</b> | <b>NAND Flash</b>    |

| K9F5616        | SAMSUNG        | NAND5616        | NAND Flash           |

| K9F8G08        | SAMSUNG        | NAND8G08        | NAND Flash, 4KB Page |

| K9G8G08        | SAMSUNG        | NAND2G08        | NAND Flash, 2KB Page |

| K9GA08U0D      | SAMSUNG        | NANDLG08XS      | NAND Flash, 4K/218B  |

| K9HBG08U       | SAMSUNG        | NANDLG08        | NAND Flash           |

| K9HC08U0       | SAMSUNG        | NANDLG08        | NAND Flash           |

| K9HC08U1M      | SAMSUNG        | NANDLG08XS      | NAND Flash, 4K/218B  |

| K9K1208X0C     | SAMSUNG        | NAND1208L       | NAND Flash           |

Its location in the TRACE32 demo folder is defined by the number of data I/O pins between the NAND flash controller and the flash device. E.g. is there are 8 data I/O pins between the NAND flash controller and the flash device the algorithm can be found in:

~~/demo/<architecture>/flash/byte/<nand\_flash\_code>.bin

This flash programming algorithm is downloaded to a target RAM when flash programming is performed. Therefore TRACE32 PowerView needs to be informed about an appropriate RAM location by the `<code_range>` parameter of the **FLASH.TARGET** program

required size for the code is `size_of(file) + 32 byte`

|                 |                                                        |

|-----------------|--------------------------------------------------------|

| FLASH algorithm | Memory mapping for the <code>&lt;code_range&gt;</code> |

| 32 byte         |                                                        |

The parameter `<data_range>` specifies the RAM location for the data, especially

- the `<data_buffer_size>` for the programming data. Recommended buffer size is 4 KByte, smaller buffer sizes are also possible. The max. buffer size is 16 KByte

- the argument buffer for the communication between TRACE32 PowerView and the programming algorithm

- the stack

```

<data_buffer_size> =

size_of(<data_range>) - 64 byte argument buffer - 256 byte stack

```

|                                                                                                                                                   |                                                        |

|---------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

| 64 byte argument buffer                                                                                                                           | Memory mapping for the <code>&lt;data_range&gt;</code> |

| Data buffer for data transfer<br>between TRACE32 and<br>NAND FLASH algorithm<br><code>&lt;buffer_size&gt;</code> calculated as<br>described above |                                                        |

| 256 byte stack                                                                                                                                    |                                                        |

## Example

```

FLASHFILE.RESET

FLASHFILE.CONFIG 0x4E000004 0x4E000008 0x4E00000C

FLASHFILE.TARGET 0x30000000++0x1FFF 0x30002000++0x3FFF

~~/demo/arm/flash/byte/nand5608.bin

FLASHFILE.Erase 0x0--0x1FFF

FLASHFILE.LOAD boot.bin 0x0

```

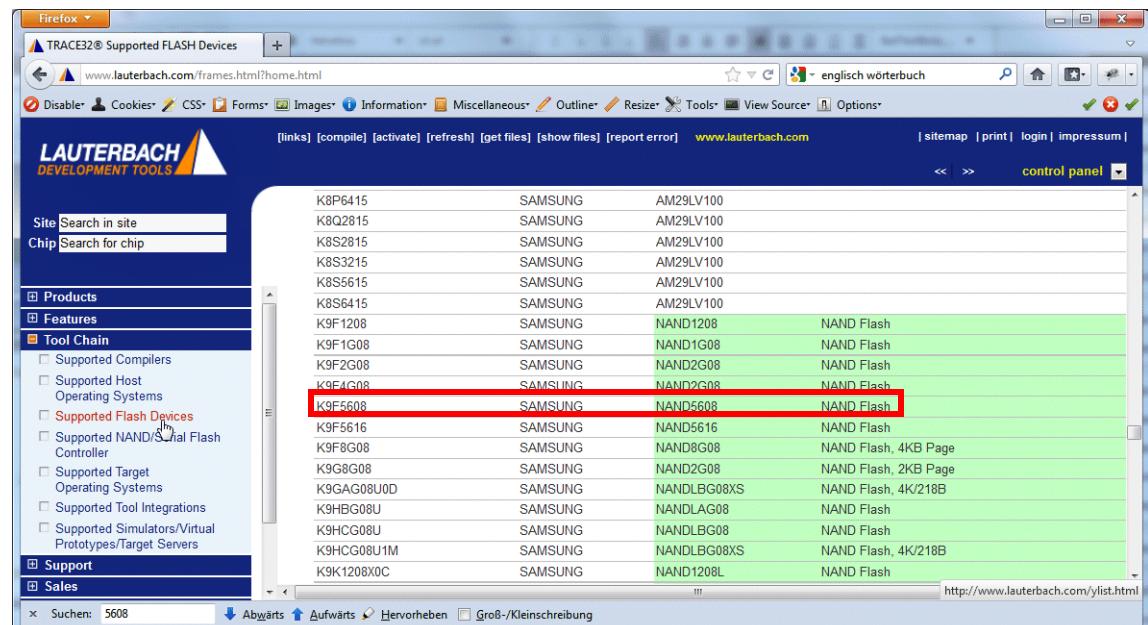

# eMMC Flash Programming

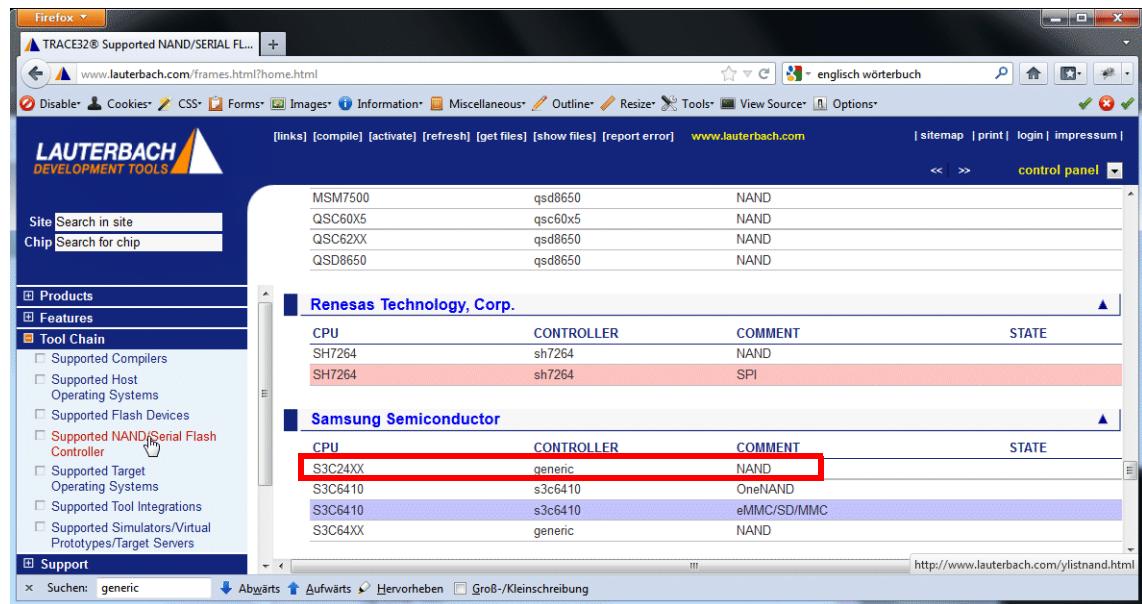

Folder and file name convention:

~~/demo/<architecture>/flash/<cpu\_name>-emmc.cmm

Get <cpu\_name> from the CPU column of the list of “**Supported NAND/Serial Flash Controller**” on the Lauterbach home page ([www.lauterbach.com](http://www.lauterbach.com)).

The screenshot shows a Firefox browser window with the Lauterbach website loaded. The URL in the address bar is <http://www.lauterbach.com/frames.html?home.html>. The page title is "TRACE32® Supported NAND/SERIAL FL...". The left sidebar has navigation links for Site Search, Chip Search, Products, Features, Tool Chain (with "Supported NAND/Serial Flash Controller" checked), Support, and a link to the list of supported controllers. The main content area is titled "Marvell, Inc." and contains a table with columns: CPU, CONTROLLER, and COMMENT. The table lists various controllers, with the row for "PXA920" highlighted in red. The table data is as follows:

| CPU     | CONTROLLER | COMMENT     |

|---------|------------|-------------|

| 88F5082 | generic    | NAND        |

| 88F5181 | generic    | NAND        |

| 88F5281 | generic    | NAND        |

| 88F6192 | generic    | NAND        |

| 88F6192 | marvell    | SPI         |

| 88F6281 | generic    | NAND        |

| 88F6281 | marvell    | SPI         |

| MV76100 | generic    | NAND        |

| MV76100 | marvell    | SPI         |

| MV78100 | generic    | NAND        |

| MV78100 | marvell    | SPI         |

| MV78200 | generic    | NAND        |

| MV78200 | marvell    | SPI         |

| PXA3XX  | pxa        | NAND        |

| PXA920  | pxa        | eMMC        |

| PXA978  | pxa        | eMMC/SD/MMC |

| PXA978  | pxa        | eMMC/SD/MMC |

Name of flash programming script here

~~/demo/arm/flash/**pxa920-emmc.cmm**

Detail on eMMC flash programming can be found in “**eMMC FLASH Programming User’s Guide**” (emmcflash.pdf).

# Establish the Communication

---

It is required to establish the communication between the debugger and the core by **SYStem.Up**. This advise the processor/chip to reset before the communication is established (details can be found on “[Establish your Debug Session](#)”, page 5).

## Load the Debug Symbols

---

```

; load debug symbols for boot loader and second stage boot loader

; address of boot loader:           0x0--0x3fff

; address of second stage boot loader: 0x33f80000++0x3ffff

; symbol mapping has to be accordingly

Data.LOAD.Elf boot.elf /NoCODE

```

If you want to debug only the second stage boot loader you can set an on-chip breakpoint to its start address:

```

Break.Set start_boot2 /Onchip

```

# Debug Scenario 3

The application (and/or the operating system) under debug are running out of RAM and a ready-to-run boot loader configures the target system and especially the RAM for this debug scenario.

\*Considering the circumstance that a process has to be started manually e.g. via a TERMINAL window

# Run the Boot Loader

---

The most important command to run the boot loader are:

|                                  |                                                        |

|----------------------------------|--------------------------------------------------------|

| <b>Go</b>                        | Start program execution                                |

| <b>Break</b>                     | Stop program execution                                 |

| <b>WAIT &lt;time&gt;</b>         | Wait the defined time (for scripts only)               |

| <b>Go &lt;address&gt;</b>        | Run the program until the specified address is reached |

| <b>Break.Set &lt;address&gt;</b> | Set a breakpoint to the specified address              |

## Example 1

```

Go ; start the program execution

Break ; stop the program execution after

; the target initialization is done

```

## Example 2

```

; ...

; script example

Go ; start the program execution

WAIT 0.5s ; wait 500. ms

Break ; stop the program execution

; ...

; continue with other setups

```

## Example 3

```

Go 0xc0001000 ; run the program until the

; complete setup is done

```

## Example 4

```

Break.Set 0xc0001000 ; set a breakpoint to the end

; of the boot loader

Go ; start the program execution

WAIT !STATE.RUN() ; wait until the program stops

; at the end of the boot loader

; ...

; continue with other setups

```

# Load Application (and/or OS) Code and Debug Symbols

---

If the boot loader does not load the application (and/or OS) you can perform the loading by the following command:

```

Data.LOAD.Elf my_app.elf

```

## Load Debug Symbols only

---

If the boot loader loads the application (and/or OS) code to RAM you need only to load the debug symbols.

```

Data.LOAD.Elf my_app.elf /NoCODE

```

## Configure the TRACE32 OS Awareness

---

Refer to [“The TASK.CONFIG Command”](#), page 8 for details.

## Complete Setup Example

---

Example for a boot loader that loads the application to RAM.

```

SYStem.CPU

SYStem.Up

Go                      ; start the program execution

WAIT 0.5s                ; wait 500. ms

Break                   ; stop the program execution

Data.LOAD.Elf my_app /NoCODE

```

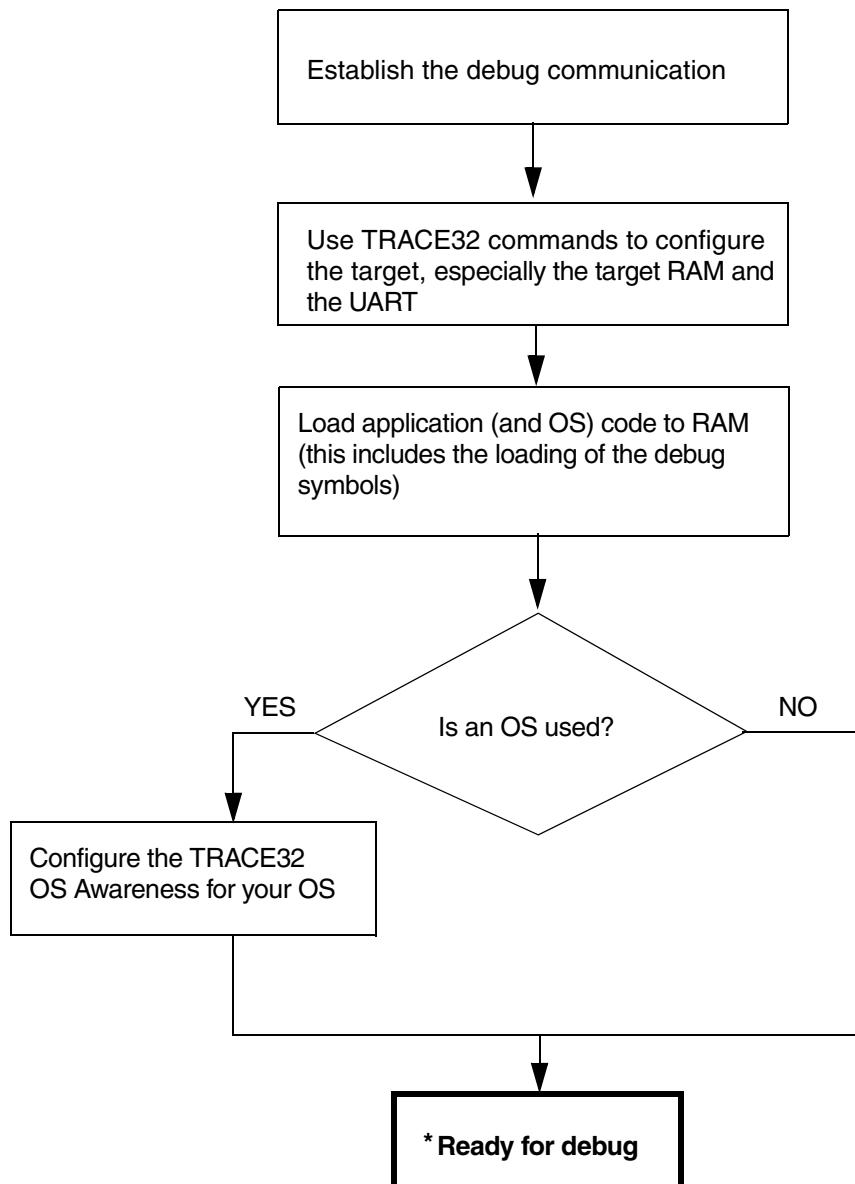

# Debug Scenario 4

The application (and the operating system) under debug are running out of RAM. The target configuration, especially the RAM configuration has to be done by TRACE32 commands, because there is no ready-to-run boot loader.

\*Considering the circumstance that a process has to be started manually e.g. via a TERMINAL window

## Write a Script to Configure the Target

---

A minimum target configuration has to configure all used memories and the serial interface.

Use the **PER.Set/PER.view** commands for this setup.

## Load Application (and/or OS) Code and Debug Symbols

---

```

Data.LOAD.Elf my_app.elf

```

## Configure the TRACE32 OS Awareness

---

Refer to “[The TASK.CONFIG Command](#)”, page 8 for details.

# Start-Up Scripts

---

It is strongly recommended to summarize the commands used to set up the debug environment in a start-up script. For this purpose, the script language PRACTICE is provided.

The standard extension for a script file is .cmm.

## Write a Start-Up Script

---

The debugger provides an PRACTICE script editor, that allows to write, to run and to debug a start-up script. The editor window provides syntax highlighting, configurable auto-indentation as well as multiple undo and redo.

**PEDIT** <file>

Open <file> with the script editor

```

PEDIT my_startup.cmm

```

The debugger provides two commands, that allow you to convert debugger configuration information to a script.

**STOre** <file> [<item>]

Generate a script that allows to reproduce the current settings

**ClipSTOre** [<item>]

Generate a command list in the clip-text that allows to reproduce the current settings

```

STOre system_settings.cmm SYSTEM

```

; Generate a script that allows you

; to reproduce the settings of the

; SYSTEM window at any time

```

PEDIT system_settings.cmm

```

; Open the file system\_settings.cmm

```

ClipSTOre SYSTEM

```

; Generate a command list that

; allows you to reproduce the

; settings of the SYSTEM window

; at any time

; The generated command list can be

; pasted in any editor

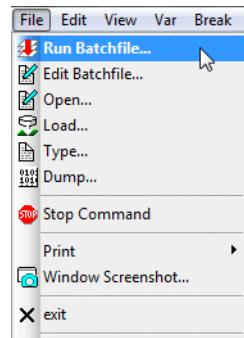

# Run a Start-up Script

---

You can run a PRACTICE script from the TRACE32 PowerView interface by selecting the menu “**File**” > “**Run Script...**”. This action corresponds to using the TRACE32 command **DO** with the script name as parameter.

|                        |                     |

|------------------------|---------------------|

| <b>DO &lt;file&gt;</b> | run PRACTICE script |

|------------------------|---------------------|

**Example:**

```

DO my_startup.cmm

```

Alternatively, you can select the “**File**” > “**ChangeDir and Run Script...**”. The difference here is that TRACE32 PowerView will change the current working directory to the directory of the selected file before running the script.

|                              |                                 |

|------------------------------|---------------------------------|

| <b>ChDir.DO &lt;file&gt;</b> | Change directory and run script |

|------------------------------|---------------------------------|

**Example:**

```

ChDir.DO C:\my_scripts\my_startup.cmm

```

## Automated Start-up Scripts

---

When a TRACE32 instance starts, the PRACTICE script **autostart.cmm** is executed, which then calls the following scripts:

- **system-settings.cmm** (from the TRACE32 system directory, usually C:\T32)

- **user-settings.cmm** (from the user settings directory: on Windows %APPDATA%\TRACE32 or ~/.trace32 otherwise)

- **work-settings.cmm** (from the current working directory)

With the command line option **-s <startup\_script>** you can specify an additional PRACTICE script (\*.cmm) which is automatically started afterwards.

**Example:**

```

C:\T32\t32arm.exe -s C:\my_scripts\start.cmm

```