# Simulator for H8/300, H8/300H and H8S

MANUAL

# Simulator for H8/300, H8/300H and H8S

---

[TRACE32 Online Help](#)

[TRACE32 Directory](#)

[TRACE32 Index](#)

|                                                             |                                                                                     |    |

|-------------------------------------------------------------|-------------------------------------------------------------------------------------|----|

| <a href="#">TRACE32 Documents</a> .....                     |  |    |

| <a href="#">TRACE32 Instruction Set Simulators</a> .....    |  |    |

| <a href="#">Simulator for H8/300, H8/300H and H8S</a> ..... | 1                                                                                   |    |

| <a href="#">TRACE32 Simulator License</a> .....             | 4                                                                                   |    |

| <a href="#">Quick Start of the Simulator</a> .....          | 5                                                                                   |    |

| <a href="#">Peripheral Simulation</a> .....                 | 7                                                                                   |    |

| <a href="#">Troubleshooting</a> .....                       | 7                                                                                   |    |

| <a href="#">FAQ</a> .....                                   | 7                                                                                   |    |

| <a href="#">Specific SYStem Commands</a> .....              | 8                                                                                   |    |

| SYStem.CONFIG                                               | Configure debugger according to target topology                                     | 8  |

| SYStem.CPU                                                  | CPU type                                                                            | 8  |

| SYStem.LOCK                                                 | Lock and tristate the debug port                                                    | 8  |

| SYStem.MemAccess                                            | Select run-time memory access method                                                | 9  |

| SYStem.Mode                                                 | Establish the communication with the simulator                                      | 9  |

| SYStem.Option.Advanced                                      | Advanced addressing mode                                                            | 10 |

| SYStem.Option.EXR                                           | EXR mode setting                                                                    | 10 |

| SYStem.Option.IMASKASM                                      | Disable interrupts while single stepping                                            | 10 |

| SYStem.Option.IMASKHLL                                      | Disable interrupts while HLL single stepping                                        | 11 |

| <a href="#">CPU specific TrOnchip Commands</a> .....        | 12                                                                                  |    |

| TrOnchip                                                    | Onchip triggers                                                                     | 12 |

| <a href="#">Memory Classes</a> .....                        | 13                                                                                  |    |

# Simulator for H8/300, H8/300H and H8S

Version 06-Jun-2024

All general commands are described in the [“PowerView Command Reference”](#) (ide\_ref.pdf) and [“General Commands Reference”](#).

# TRACE32 Simulator License

---

[build 68859 - DVD 02/2016]

The extensive use of the TRACE32 Instruction Set Simulator requires a *TRACE32 Simulator License*.

For more information, see [www.lauterbach.com/sim\\_license.html](http://www.lauterbach.com/sim_license.html).

# Quick Start of the Simulator

## To start the simulator, proceed as follows:

1. Select the device prompt for the Simulator and reset the system.

```

B:::

RESet

```

The device prompt B:: is normally already selected in the [TRACE32 command line](#). If this is not the case, enter B:: to set the correct device prompt. The [RESet](#) command is only necessary if you do not start directly after booting TRACE32.

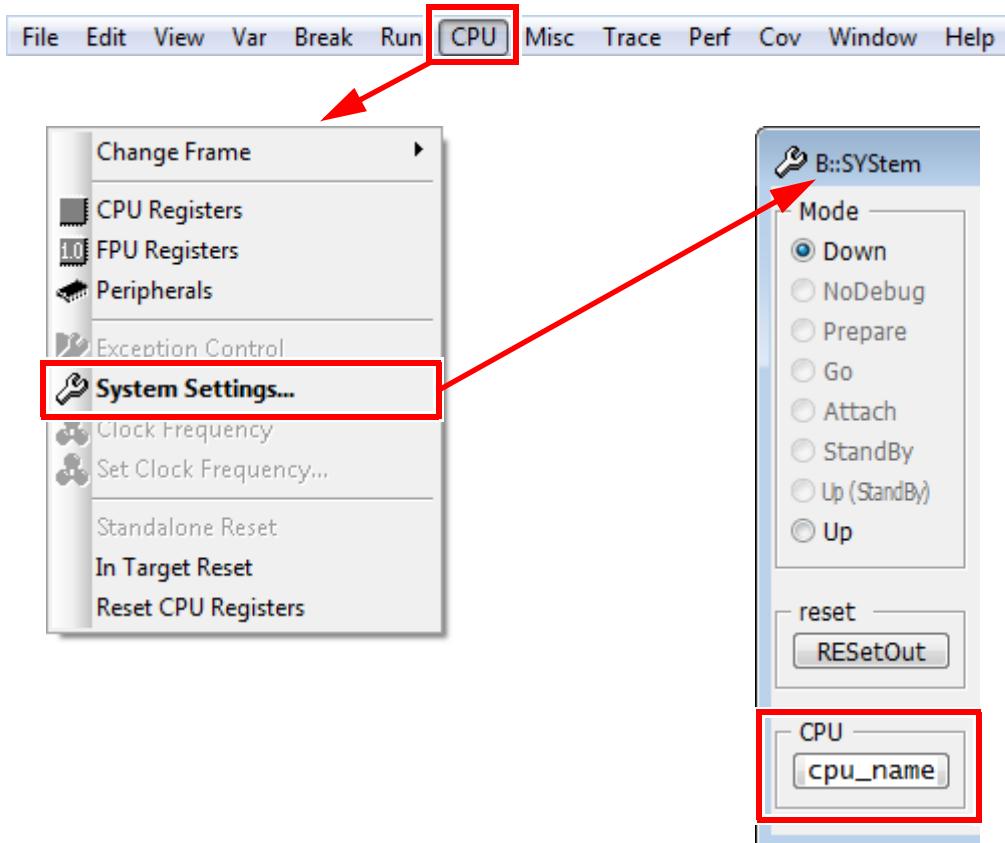

2. Specify the CPU specific settings.

```

SYStem.CPU <cpu_name>

```

The default values of all other options are set in such a way that it should be possible to work without modification. Please consider that this is probably not the best configuration for your target.

3. Enter debug mode.

```

SYStem.Up

```

This command resets the CPU and enters debug mode. After this command is executed it is possible to access memory and registers.

4. Load the program.

```

Data.LOAD.<file_format> <file> ; load program and symbols

```

See the **Data.LOAD** command reference for a list of supported file formats. If uncertain about the required format, try **Data.LOAD.auto**.

A detailed description of the **Data.LOAD** command and all available options is given in the reference guide.

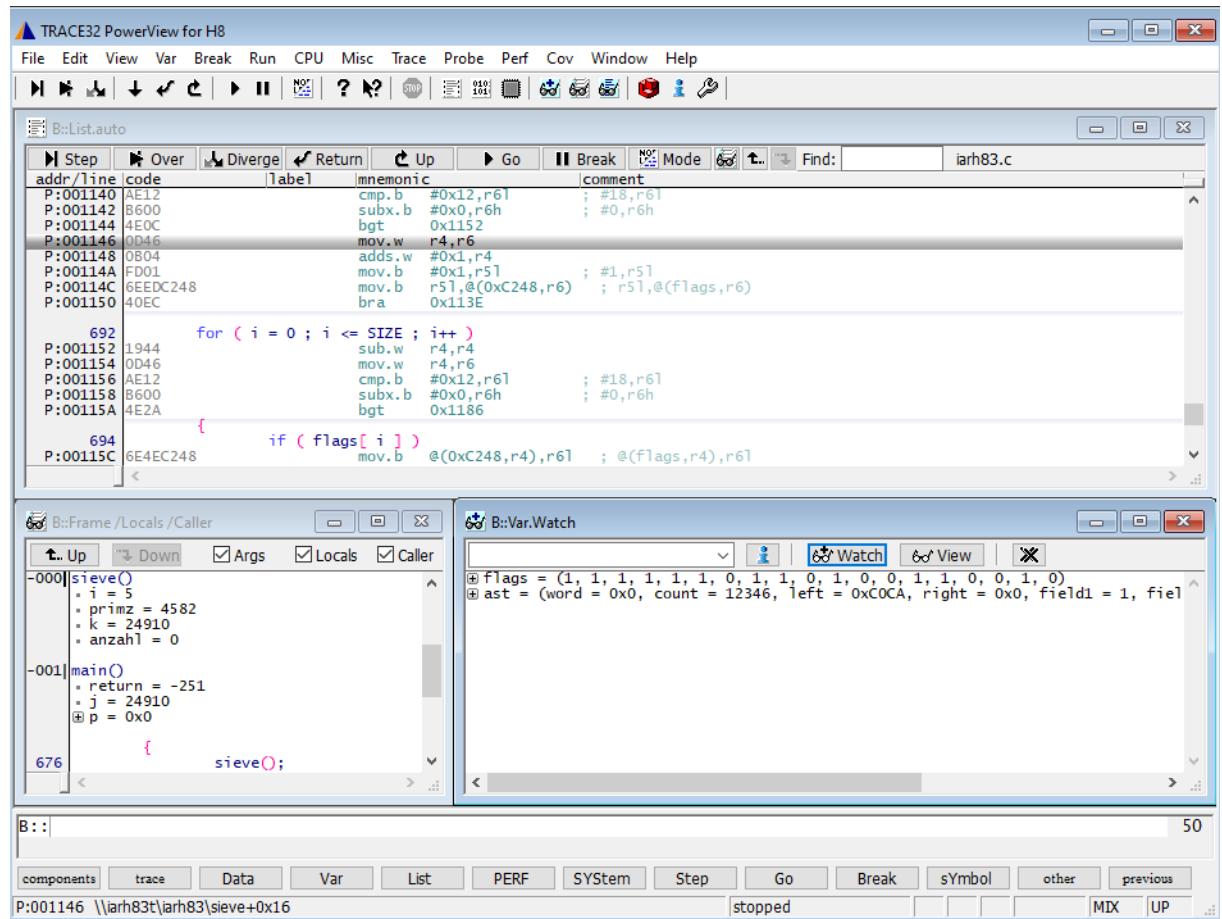

5. Start-up example

A typical start sequence is shown below. This sequence can be written to a PRACTICE script file (\*.cmm, ASCII format) and executed with the command **DO <file>**.

```

B::: ; Select the ICD device prompt

WinCLEAR ; Clear all windows

SYStem.CPU <cpu_name> ; Select CPU type

SYStem.Up ; Reset the target and enter

; debug mode

Data.LOAD.<file_format> <file> ; Load the application

Register.Set pc main ; Set the PC to function main

PER.view ; Show clearly arranged

; peripherals in window *) */

List.Mix ; Open source code window *) */

Register.view /SpotLight ; Open register window *) */

Frame.view /Locals /Caller ; Open the stack frame with

; local variables *) */

Var.Watch %Spotlight flags ast ; Open watch window for

; variables *) */

```

\*) These commands open windows on the screen. The window position can be specified with the **WinPOS** command.

For more information, see “[API for TRACE32 Instruction Set Simulator](#)” (simulator\_api.pdf).

## Troubleshooting

---

No information available.

## FAQ

---

Please refer to <https://support.lauterbach.com/kb>.

# Specific SYStem Commands

---

## SYStem.CONFIG

Configure debugger according to target topology

---

The **SYStem.CONFIG** commands have no effect on the simulator. They are only provided to allow the user to run PRACTICE scripts written for the debugger within the simulator without modifications.

## SYStem.CPU

CPU type

---

Format: **SYStem.CPU <type>**

*<mode>*: **H83001 | H83002 ...**

Selects the processor type. The ROM monitor software requires also a modification in the configuration table for different processor types.

## SYStem.LOCK

Lock and tristate the debug port

---

Format: **SYStem.LOCK [ON | OFF]**

The command has no effect for the simulator.

Format: **SYStem.MemAccess Enable | StopAndGo | Denied**

**SYStem.ACCESS** (deprecated)

|                         |                                                                                                                                                                                                               |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Enable</b>           | Real-time memory access during program execution to target is enabled.                                                                                                                                        |

| <b>CPU</b> (deprecated) |                                                                                                                                                                                                               |

| <b>Denied</b>           | Real-time memory access during program execution to target is disabled.                                                                                                                                       |

| <b>StopAndGo</b>        | Temporarily halts the core(s) to perform the memory access. Each stop takes some time depending on the speed of the JTAG port, the number of the assigned cores, and the operations that should be performed. |

## SYStem.Mode

## Establish the communication with the simulator

Format: **SYStem.Mode <mode>**

**SYStem.Down** (alias for SYStem.Mode Down)

**SYStem.Up** (alias for SYStem.Mode Up)

<mode>: **Down**

**NoDebug**

**Go**

**Up**

Default: Down.

Selects the target operating mode.

|                |                                                                                                                                                  |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Down</b>    | The CPU is in reset. Debug mode is not active. Default state and state after fatal errors.                                                       |

| <b>NoDebug</b> | The CPU is running. Debug mode is not active. Debug port is tristate. In this mode the target should behave as if the debugger is not connected. |

**Go** The CPU is running. Debug mode is active. After this command the CPU can be stopped with the break command or if any break condition occurs.

**Up** The CPU is not in reset but halted. Debug mode is active. In this mode the CPU can be started and stopped. This is the most typical way to activate debugging.

If the mode **Go** is selected, this mode will be entered, but the control button in the **SYStem.state** window jumps to the mode **Up**.

## **SYStem.Option.Advanced**

Advanced addressing mode

Format: **SYStem.Option.Advanced [ON | OFF]**

Defines the address mode of the CPU.

**off** Normal address mode (64K).

**on** Advanced address mode (16M).

## **SYStem.Option.EXR**

EXR mode setting

Format: **SYStem.Option.EXR [ON | OFF]**

TBD.

## **SYStem.Option.IMASKASM**

Disable interrupts while single stepping

Format: **SYStem.Option.IMASKASM [ON | OFF]**

Default: OFF.

If enabled, the interrupt mask bits of the CPU will be set during assembler single-step operations. The interrupt routine is not executed during single-step operations. After single step the interrupt mask bits are restored to the value before the step.

Format: **SYStem.Option.IMASKHLL [ON | OFF]**

Default: OFF.

If enabled, the interrupt mask bits of the CPU will be set during HLL single-step operations. The interrupt routine is not executed during single-step operations. After single step the interrupt mask bits are restored to the value before the step.

## TrOnchip

## Onchip triggers

---

This command group has no effect on the TRACE32 Instruction Set Simulator.

# Memory Classes

---

| Memory Class | Description |

|--------------|-------------|

| D            | Data        |

| P            | Program     |